当前位置:网站首页>Method of using inout signal in Verilog

Method of using inout signal in Verilog

2022-06-22 15:13:00 【Zi Mu】

Catalog

One 、inout How to use it in design documents

1.1、inout The first way to use

1.2、inout The second use of the implementation

Two 、inout How to use it in simulation test

One 、inout How to use it in design documents

stay FPGA In the design process of , Sometimes we encounter two-way signals ( It can be used as output , Signals that can also be used as inputs are called bidirectional signals ). such as ,IIC In the bus SDA A signal is a two-way signal ,QSPI Flash During the four wire operation of the, the four signal lines are bidirectional signals . stay Verilog Keyword in inout Define bidirectional signals , Here is a summary of bidirectional signal processing methods .

1.1、inout The first way to use

actually , The essence of bidirectional signal is composed of a three state gate , Three state gate can output high level , Low level and high resistance states , stay FPGA in , The structure of a three state gate is shown in the figure below :

Describing this logic Verilog The code is as follows :

module inout_top

(

input I_data_in ,

inout IO_data ,

output O_data_out ,

input Control

);

assign IO_data = Control ? I_data_in : 1'bz ;

assign O_data_out = IO_data ;

endmoduleWhen Control by 1 when ,IO_data For export , Output I_data_in Value

When Control by 0 when ,IO_data For input , Assign the input signal to O_data_out

This code is in Vivado2015.4.2 Compilation environment RTL The picture is shown below

stay ISE14.7 Under the compilation environment of RTL The picture is shown below

It can be found in Vivado2015.4.2 Environmental Control The signal IBUF There's also a LUT, stay ISE14.7 In the environment Control A reverser is synthesized behind the signal , There's this LUT And the reason for the inverter is Control by 1 Only then IO_data Set to output , And in the Xilinx In a IOBUF Resource default T intention 0 when IO End is output ,T intention 1 when ,IO End as input , So the

assign IO_data = Control ? I_data_in : 1'bz ;//Control=1 when As the output Change it to

assign IO_data = (Control == 1’b0) ? I_data_in : 1'bz ;//Control=0 when As the output stay Vivado2015.4.2 Integrated under the environment RTL Figure below

stay ISE14.7 Under the environment of RTL The picture is shown below

obviously ,Vivado Environment LUT and ISE The inverter in the environment is missing , Saved 1 individual Cell resources .

1.2、inout The second use of the implementation

The above is the treatment inout The first way , The second treatment inout The way to signal is to call Xilinx Of IOBUF The original language ,IOBUF The primitive of can be found in Vivado2015.4.2 Of Language Templates Find .

Call the of this primitive Verilog The code is as follows :

module inout_top

(

input I_data_in,

inout IO_data ,

output O_data_out ,

input Control

);

IOBUF #(

.DRIVE(12), // Specify the output drive strength

.IBUF_LOW_PWR("TRUE"), // Low Power - "TRUE", High Performance = "FALSE"

.IOSTANDARD("DEFAULT"), // Specify the I/O standard

.SLEW("SLOW") // Specify the output slew rate

) IOBUF_inst (

.O(O_data_out), // Buffer output

.IO(IO_data), // Buffer inout port (connect directly to top-level port)

.I(I_data_in), // Buffer input

.T(Control) // 3-state enable input, high=input, low=output

);

endmodulestay Vivado2015.4.2 Integrated under the environment RTL The picture is shown below

stay ISE14.7 Integrated under the environment RTL The picture is shown below

Obviously and assign IO_data = (Control == 1’b0) ? I_data_in : 1'bz ; In this case, a comprehensive RTL Exactly the same as .

1.3、inout Use summary

utilize Verilog There are two ways to process bi-directional signals :

1、 Write code

assign IO_data = (Control == 1’b0)? I_data_in : 1'bz ;

assign O_data_out = IO_data ;2、 Exemplification IOBUF The original language

IOBUF #(

.DRIVE(12), // Specify the output drive strength

.IBUF_LOW_PWR("TRUE"), // Low Power - "TRUE", High Performance = "FALSE"

.IOSTANDARD("DEFAULT"), // Specify the I/O standard

.SLEW("SLOW") // Specify the output slew rate

) IOBUF_inst (

.O(O_data_out), // Buffer output

.IO(IO_data), // Buffer inout port (connect directly to top-level port)

.I(I_data_in), // Buffer input

.T(Control) // 3-state enable input, high=input, low=output

);Two 、inout How to use it in simulation test

Verilog Use in inout How to write and simulate - Baidu library

边栏推荐

- Thoroughly understand the factory mode

- How to compare the size of two dates in unity and C #

- [Software Engineering] acquire requirements

- C generic_ Generic class

- I took a private job and earned 15250. Is it still necessary to do my main business?

- Struggle, programmer -- Chapter 48 A thousand gold coins are bought like Fu. Who can complain about this situation

- C # paging calculation total pages, current page data set

- Error: Unable to find a match: lrzsz的解决方法

- 好风凭借力 – 使用Babelfish 加速迁移 SQL Server 的代码转换实践

- [PR] basic process

猜你喜欢

![[Software Engineering] design module](/img/08/d55af729a8241e109fdeb96c896670.png)

[Software Engineering] design module

C language student management system (open source)

Please, don't be brainwashed. This is the living reality of 90% of Chinese people

Zhongshanshan: engineers after being blasted will take off | ONEFLOW u

数据库连接池:压力测试

C语言学生管理系统(开源)

那些令人懵逼的用户态&内核态

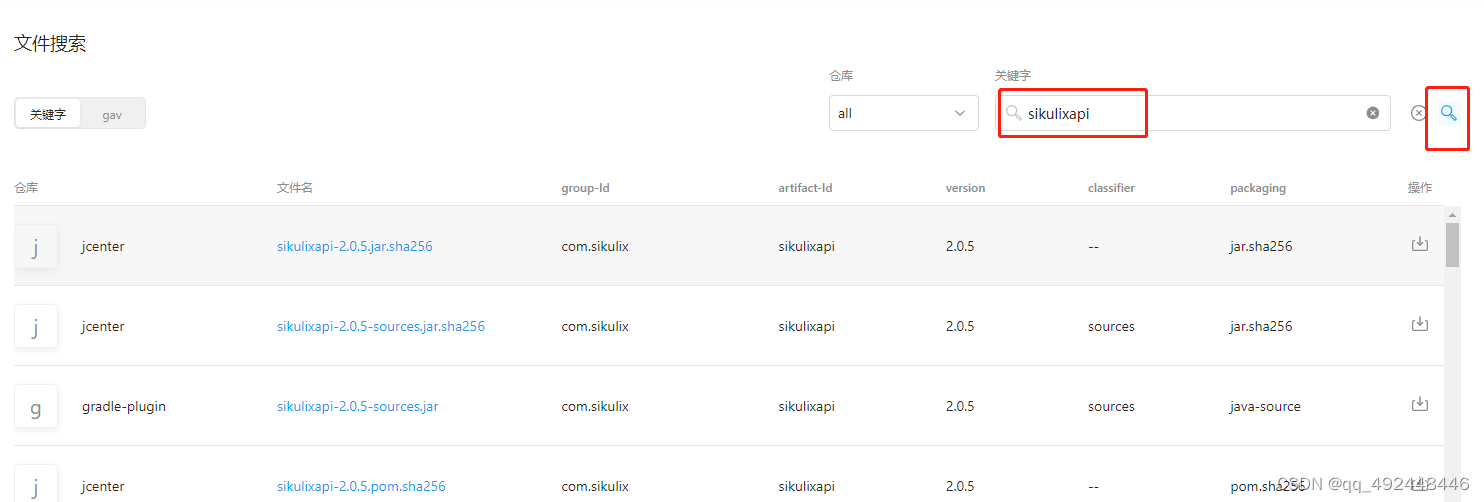

Using pictures to locate app elements sikulix

After 17 years, Liu Yifei became popular again: ordinary people don't want to be eliminated, but they also need to understand this

嵌入式中的强符号和弱符号是什么?

随机推荐

[live broadcast review] battle code pioneer phase VI: build a test subsystem and empower developers to provide

Error: Unable to find a match: lrzsz的解决方法

Database connection pool: Code Directory

Using virtual serial port to debug serial port in keil MDK

Software architecture

Front and back management system of dessert beverage store based on SSM framework dessert mall cake store [source code + database]

Once, I had 5 part-time jobs just to buy a new earring for my girlfriend

We will resolutely fight and win the hard battle of flood control and disaster relief and spare no effort to ensure the safety of people's lives and property

Groovy之列表操作

2022年失业的人多吗?今年是不是特别难找工作?

那些令人懵逼的用户态&内核态

What does password security mean? What are the password security standard clauses in the ISO 2.0 policy?

Go all out to implement the flood control and disaster relief measures in detail and in place, and resolutely protect the safety of people's lives and property

U++编程 数组学习笔记

Mysql学习笔记2022

轻松上手Fluentd,结合 Rainbond 插件市场,日志收集更快捷

Detailed explanation of CSAPP Labs

【浙江大学】考研初试复试资料分享

Network address translation nat

Le modèle de diffusion est encore fou! Cette fois - ci, la zone occupée était...