当前位置:网站首页>jvm-02. Guarantee of orderliness

jvm-02. Guarantee of orderliness

2022-06-23 05:56:00 【CaptainCats】

Order guarantees

Hardware level order guarantee

Instruction rearrangement improves operation efficiency , But it also brings about the problem of inconsistent execution data ,

How to ensure order at the hardware level ?

CPU Memory barrier

Write barriers sfence

stay sfence The write operation before the instruction must be in sfence Before the subsequent write operation

Reading barrier lfence

stay lfence The read operation before the instruction must be in lfence Before the read operation after

Hybrid barrier mfence

stay mfence The read / write operation before the instruction must be in mfence Before the subsequent read / write operation

Instructions before and after the barrier cannot be rearranged , This is a CPU Level memory barrier .

Atomic directive

x86 Upper "lock" Instructions ,lock…doSth…lock It's an instruction ,

lock Followed by other instructions ,

During the execution of this instruction , This memory cannot be modified by other instructions , To ensure the order of execution .

Jvm Memory barrier

Jvm Software level , Its memory barrier depends on hardware ,

It combines reading and writing in pairs , Four memory barriers are formed :

LoadLoad barrier

For statements like this Load1;LoadLoad;load2;

stay Load2 And before subsequent read operations , Make sure that Load1 The data to be read is read .

StoreStore barrier

For statements like this Store1;StoreStore;Store2;

stay Store2 And subsequent write operations before execution , Make sure that Store1 Is visible to other processors .

LoadStore barrier

For statements like this Load1;LoadStore;Store2;

stay Store2 And subsequent write operations before execution , Make sure that Load1 The data to be read is read .

StoreLoad barrier

For statements like this Store1;StoreLoad;load2;

stay load2 And before subsequent read operations , Make sure that Store1 Is visible to other processors .

Volatile

stay jvm At the implementation level of ,volatile The read and write of the memory area are shielded :

In the face of volatile The write operation of the modified variable is preceded by StoreStore barrier , I added StoreLoad barrier ,

In the face of volatile The read operation of the modified variable is preceded by LoadLoad barrier , I added LoadStore barrier .

Synchronized

Synchronized The corresponding is C and C++ Called the synchronization mechanism provided by the operating system ,

Depending on the hardware CPU, stay CPU The level is to use lock Instructions to achieve .

边栏推荐

- Real MySQL interview question (23) -- pinduoduo ball game analysis

- MDM data cleaning function development description

- visdom的使用

- Wechat applet: wechat can also send flash photos to create wechat applet source code download and customize flash time

- vant weapp日历组件性能优化 Calendar 日历添加min-date最小日期页面加载缓慢

- 技能自检 | 想当测试Leader,这6项技能你会吗?

- Adnroid activity screenshot save display to album view display picture animation disappear

- Leetcode topic analysis: factorial training zeroes

- PAT 乙等 1022 D进制的A+B

- Addressing and addressing units

猜你喜欢

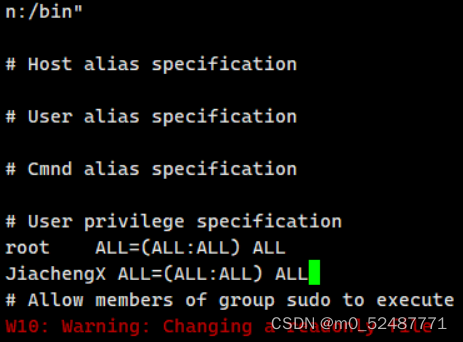

如何指定pig-register项目日志的输出路径

Raspberry pie assert preliminary exercise

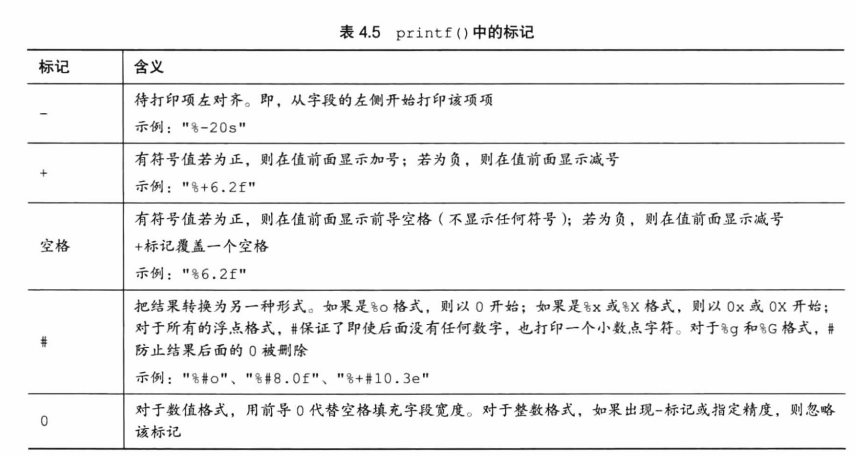

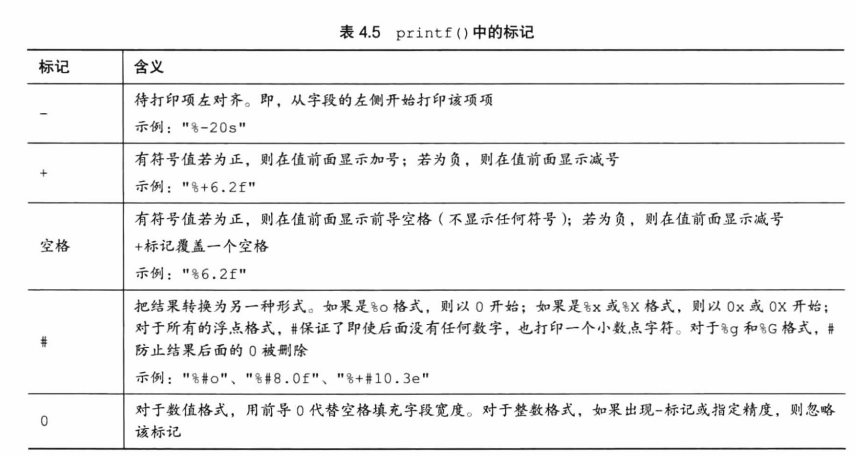

C primer plus learning notes - 2. Constant and formatted IO (input / output)

Opportunities and challenges of digital collections from the perspective of technology development team

C prime plus notes d'apprentissage - 2, constantes et formatage io (I / o)

True MySQL interview question (24) -- row column exchange

Software design and Development Notes 2: serial port debugging tool based on QT design

How can digital collections empower economic entities?

Three most advanced certifications, two innovative technologies and two outstanding cases, Alibaba cloud appeared at the cloud native industry conference

数字藏品火热背后需要强大的技术团队支持 北方技术团队

随机推荐

【斯坦福计网CS144项目】Lab2: TCPReceiver

Prometheus, incluxdb2.2 installation and flume_ Export download compile use

Excel sheet column title for leetcode Title Resolution

[graduation season u; advanced technology Er] farewell to the confused self in the past two years. Regroup, junior I'm coming

Activity startup mode and life cycle measurement results

jvm-04.对象的内存布局

Special research on Intelligent upgrading of heavy trucks in China in 2022

Wechat applet: Star Trek spaceship ticket production and generation

jvm-01.指令重排

Alibaba cloud object storage oss+picgo+typera implements the construction map

Lottery DDD code

Huawei's software and hardware ecosystem has taken shape, fundamentally changing the leading position of the United States in the software and hardware system

使用链表实现两个多项式相加和相乘

MySQL面试真题(三十)——贝壳-房产订单分析

Wechat applet: production and generation of love guarantee

【owt】owt-client-native-p2p-e2e-test vs2017构建 6:修改脚本自动生成vs工程

Three most advanced certifications, two innovative technologies and two outstanding cases, Alibaba cloud appeared at the cloud native industry conference

工作积累-判断GPS是否打开

jvm-02.有序性保证

PAT 乙等 1021 个位数统计