当前位置:网站首页>Axi DMA IP core operation process

Axi DMA IP core operation process

2022-06-24 21:09:00 【yindq1220】

Direct register mode

visit DMACR,SA,DA,length Register initialization DMA transmission , When the transfer is complete , Of related channels DMASR.IOC_Irq It works ( The premise is to enable the interrupt ,DMACR.IOC_IrqEn Can make ).

MM2S Channel start process :

- MM2S_DMACR.RS=1, function DMA

- Can make MM2S_DMACR.IOC_IrqEn and MM2S_DMACR.Err_IrqEn

- Configure valid MM2S_SA and MM2S_SA_MSB register

- Write a non-zero value to MM2S_LENGTH register , Start reading DDR Sent to the AXIS port . This value is the number of bytes read from memory

S2MM Channel start process :

- S2MM_DMACR.RS=1, function DMA

- Can make S2MM_DMACR.IOC_IrqEn and S2MM_DMACR.Err_IrqEn

- Configure valid S2MM_DA and S2MM_SA_MSB register

- Write a non-zero value to S2MM_LENGTH register , start-up AXIS Port data write DDR. This value must be greater than or equal to the number of bytes of a packet of data .

In direct register mode , The above startup process needs to be recycled , Every time I read and write , The above registers need to be reconfigured .

The end of each process , An interrupt notification will occur CPU Data operation completed , need CPU eliminate IOC_Irq Register interrupt flag .

SG Pattern

After configuring control registers and descriptors ,SG mode . Can greatly improve DMA performance .

MM2S Channel start process :

- To configure MM2S_CURDESC and MM2S_CURDESC_MSB register , Write the address of the start operator .

- To configure MM2S_DMACR.RS=1, function DMA

- register MM2S_DMACR.IOC_IrqEn and MM2S_DMACR.Err_IrqEn Can make

- To configure MM2S_TAILDESC and MM2S_TAILDESC_MSB, here DMA Start reading descriptors in memory

- DMA Automatically process operators and read memory data through AXIS Port output

S2MM Channel start process :

- To configure S2MM_CURDESC and S2MM_CURDESC_MSB register , Write the address of the start operator .

- To configure S2MM_DMACR.RS=1, function DMA

- register S2MM_DMACR.IOC_IrqEn and S2MM_DMACR.Err_IrqEn Can make

- To configure S2MM_TAILDESC and S2MM_TAILDESC_MSB, here DMA Start reading descriptors in memory

- DMA Automatically process operators and receive AXIS Port data is written to memory

The end of each process (DMA Received with EOF The operator of ),DMA Generate interrupt to CPU, need CPU eliminate IOC_Irq Register interrupt flag , Re operate the above process .

loop DMA Pattern

In this mode ,DMA Can handle the same buffer descriptor , There is no interruption . In this mode DMA Keep working , Unless an abnormal stop or reset occurs .

The key to this model is ,tail Descriptor pointing first The descriptor . Set up Cyclic BD Enable by 1( Need to be in DMA Configure before running ).

The rest of the process is the same as SG The pattern is the same .

边栏推荐

- It was Tencent who jumped out of the job with 26k. It really wiped my ass with sandpaper. It gave me a hand

- opds sql组件能不能将流程参数通过上下文传给下一个组件

- Web automation: summary of special scenario processing methods

- 在Dialog中使用透明的【X】叉叉按钮图片

- Common member methods of the calendar class

- Background operation retry gave up; KeeperErrorCode = ConnectionLoss

- Markdown use

- Leetcode (146) - LRU cache

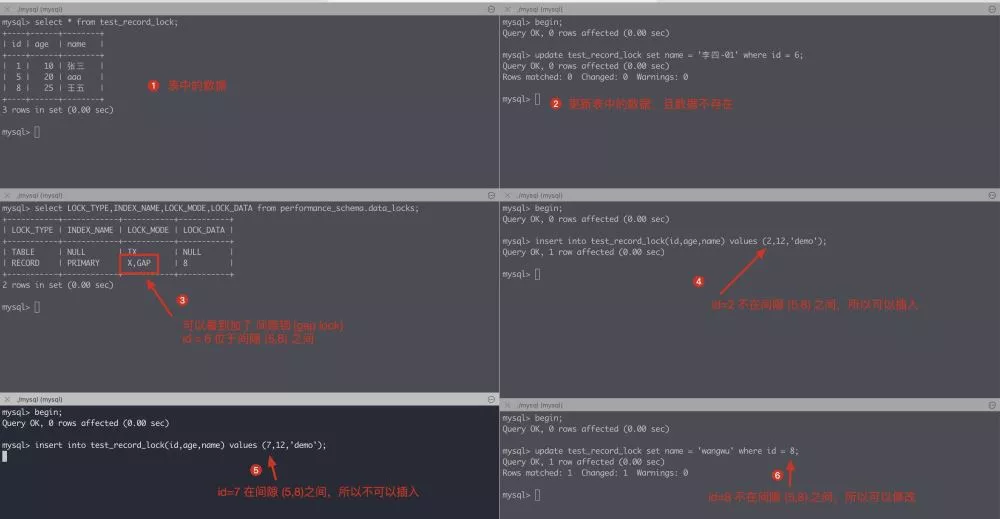

- Talking about the range of data that MySQL update will lock

- Appium desktop introduction

猜你喜欢

浅谈MySql update会锁定哪些范围的数据

Nifi fast authentication configuration

Responsibility chain mode -- through interview

The difference between RPC and restful

Learn to use a new technology quickly

主数据建设的背景

![[普通物理] 光栅衍射](/img/f3/965ff7cd3bb76b4f71b69b9d12ece3.png)

[普通物理] 光栅衍射

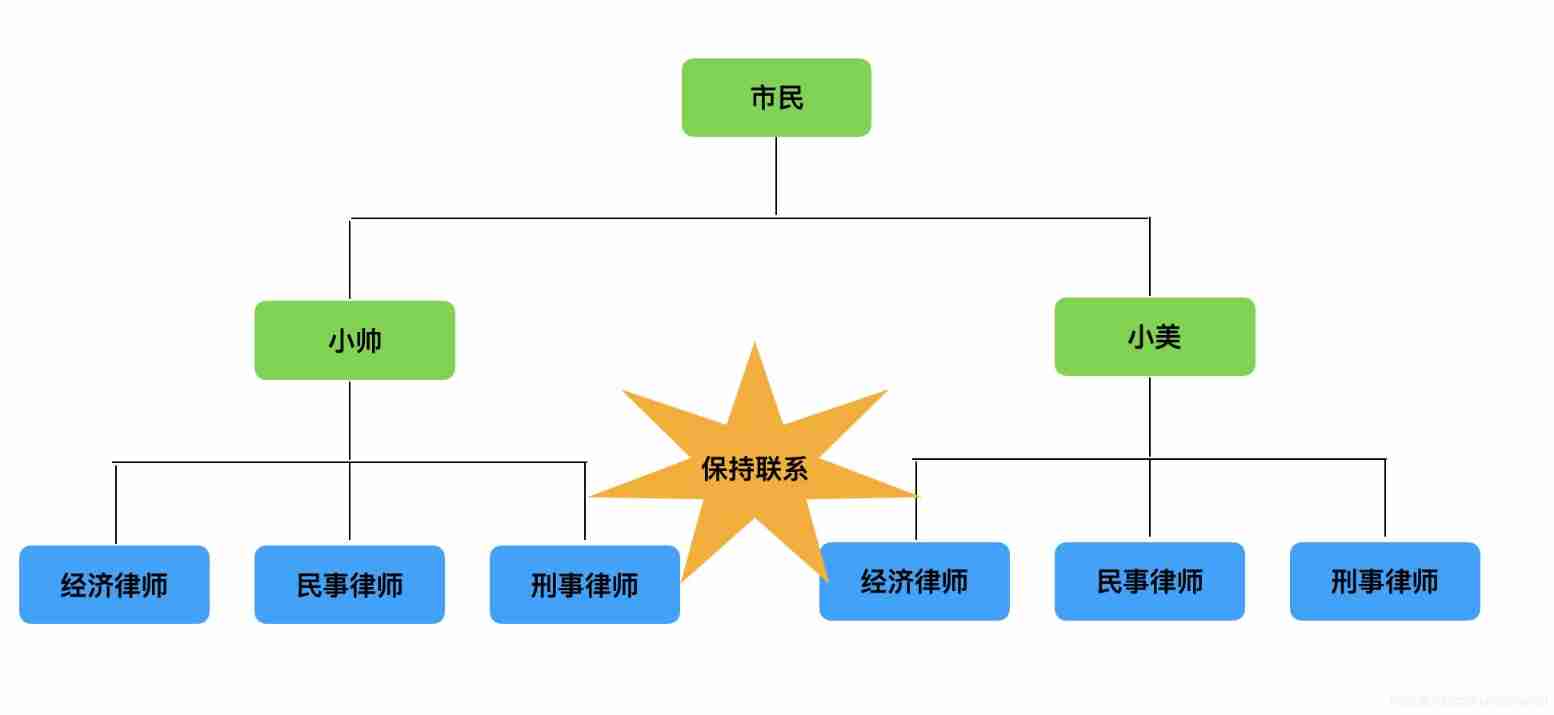

Bridging mode -- law firm

DHCP operation

Berkeley, MIT, Cambridge, deepmind and other industry leaders' online lectures: towards safe, reliable and controllable AI

随机推荐

The AI for emotion recognition was "harbouring evil intentions", and Microsoft decided to block it!

Pytest testing framework

Open function

Rename and delete files

Leetcode (135) - distribute candy

Static routing job

Create a multithreaded thread class

Why do we always "give up halfway"?

Learn together and make progress together. Welcome to exchange

Leetcode(455)——分发饼干

Common self realization functions in C language development

Set up your own website (14)

Batch capitalization of MySQL table names

It was Tencent who jumped out of the job with 26k. It really wiped my ass with sandpaper. It gave me a hand

maptalks:数据归一化处理与分层设色图层加载

What are the problems with traditional IO? Why is zero copy introduced?

Camera rental management system based on qt+mysql

The Google File System (GFS) learning notes

Summary of message protocol problems

Network security review office starts network security review on HowNet