当前位置:网站首页>Icer Skill 02makefile script Running VCS Simulation

Icer Skill 02makefile script Running VCS Simulation

2022-06-23 04:57:00 【Quatre - vingt - quatre.】

Table des matières

0.Préface

InwinEn courant.modelesimLes simulations le savent,Il nous faut deux.vDocumentation,Puis un point de fonctionnement de l'interface est venu et est allé,La forme d'onde est finalement générée,C'est très inefficace pour les développeurs,Alors aujourd'hui, NotezlinuxUtilisation suivantemakefileLe script s'est enfuivcsSimulation.

1.Options communes

| Objet | Directives | Fonction de représentation |

|---|---|---|

| vcs | -full64 | Soutien64Bits |

| vcs | -l Espaces Nom du fichier | Créer un fichier journal,En général.logDocumentation |

| vcs | -f Espaces Nom du fichier | Indexer le chemin du fichier à compiler dans un fichier,C'est possible.file.listDocumentation |

| vcs | -debug_all | Prise en charge de la mise en service |

| vcs | -timescale=1ns/1ns | Précision temporelle |

| vcs | +v2k | Verilog2001Architecture |

| vcs | -sverilog | svArchitecture |

| simv | -l | Journal de simulation |

| simv | -gui | Ouvrir l'interface |

| dve | -vpd Espaces Nom du fichier | Ouvrir le fichier Waveform,En général, un&Indique que l'arrière - plan fonctionne |

2.Travaux préparatoires

Commencez par écrire un simplemakefileScript de l'opération d'animationvcsSimulation,Bien sûr qu'il y a un certainlinux Connaissance des opérations de base , Cette commande de base est prête pour une heure et demie. ,Petitcase

① D'abord, on entre dans le terminal. ,Avecls Commande pour voir quels fichiers sont disponibles

ls

② Il n'y en a qu'un. add_vcsDossier pour

③ Ignorer ce dossier ,Reconstruire unadd_testDossier pour

mkdir add_test

④ Vous pouvez voir un dossier supplémentaire sur le Bureau ( Bien sûr, j'ai tapé le code sous le chemin du Bureau. )

⑤Entréeadd_testChemin sous le dossier

cd ./add_test/

⑥Créer deux fichiers:add.v add_tb.v

touch add.v

touch add_tb.v

⑦Utilisergvim L'éditeur écrit deux .vDocumentation,Les codes sont les suivants:

add.v

module add ( input a,b,c_in, output sum,c_out ); assign sum = a ^ b ^ c_in; assign c_out = (c_in & b)|(a & b)|(a & c_in); endmoduleadd_tb.v Assurez - vous que la simulation est terminée. , Sinon, cours. vcs Le processus sera bloqué tout le temps ,Et puis$vcdpluson Générer un fichier Waveform

`timescale 1 ns/1 ns module add_tb(); //Entréereg reg a; reg b; reg c_in; reg clk; //Produitswire wire sum; wire c_out; //Cycle d'horloge,Unitésns parameter CYCLE = 20; // Générer une horloge locale initial begin clk = 0; forever #(CYCLE/2) clk=~clk; end //Initialisation du signal initial begin #1 a = 0; b = 0; c_in = 0; end // Exemple de module à tester add u1 ( .a (a), .b (b), .c_in (c_in), .c_out (c_out), .sum (sum) ); // Attribution d'autres signaux d'entrée always @(posedge clk)begin a = {$random}%2; b = {$random}%2; c_in = {$random}%2; end initial begin $vcdpluson; end initial begin # 200 $finish; end endmodule

⑧Générerfile.listDocumentation,Réutiliserls Voir si les fichiers correspondants sont réellement générés

find -name "*.v"> file.list

⑨UtilisergvimVoirflie.listDocumentation(Appuyez surgfPeut sauter,ctrl+oRetour), La découverte est une collection de chemins relatifs

gvim file.list

3.makefileCompilation

- vcs La simulation doit d'abord être compilée (com), Puis la simulation (sim), Puis il y a la forme d'onde. (AvecdveRegarde.)

- Définissez d'abordall: com sim run_dve

- Alors écrivezcom sim run_dve Des directives

- Enfin, ajoutez unclean Pour effacer les fichiers générés par la simulation

D'abord.add_testCréer un sous le cheminmakefile Documents établis ultérieurement

Les codes sont les suivants::

all: com sim run_dve

com:

vcs -sverilog -debug_all -timescale=1ns/1ns -f file.list -l com.log

sim:

./simv -l sim.log

run_dve:

dve -vpd vcdplus.vpd &

clean:

rm -rf *.vpd csrc *.log *.key *.vdb simv* DVE*

Vous pouvez voir la fonctionnalité de chaque instruction à partir du tableau au début

4.Simulation en un clic et nettoyage des fichiers

①Retour au terminal,Inadd_testExécuter sous le chemin

make all

C'est tout.

②La simulation est illustrée ci - dessous:

③Fonctionnement automatiquedve , Nous pouvons ajouter une forme d'onde de vue

④Enfin fermédveInterface,Fonctionnement sur le terminal

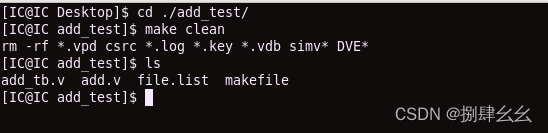

make clean

Supprimer tous les fichiers générés ,ls Regarde ce qu'il en reste. 4Fichiers

边栏推荐

猜你喜欢

ApiPost接口测试的用法之------Get

What are the types of independent station chat robots? How to quickly create your own free chat robot? It only takes 3 seconds!

一款MVC5+EasyUI企业快速开发框架源码 BS框架源码

How to make social media the driving force of cross-border e-commerce? This independent station tool cannot be missed!

Win10 view my Ini path

美团好文:从预编译的角度理解Swift与Objective-C及混编机制

Shadertoy基础教学02、画笑脸

McKinsey: in 2021, the investment in quantum computing market grew strongly and the talent gap expanded

Usage of apipost interface test ------ get

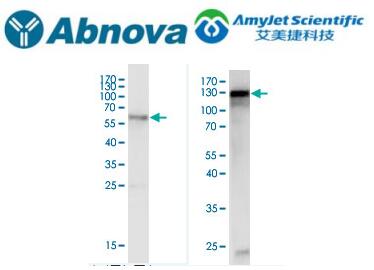

Abnova ACTN4纯化兔多克隆抗体说明书

随机推荐

PCB----理论与现实的桥梁

Const understanding II

Experience of Tencent cloud installed by Kali

电流继电器JDL-1002A

Abnova 荧光染料 555-C3 马来酰亚胺方案

ApiPost接口测试的用法之------Post

CAN总线基础知识

const理解之一

重装Cadence16.3,失败与成功

Static two position relay xjls-84/440/dc220v

Principle of 8-bit full adder

在Pycharm中对字典的键值作更新时提示“This dictionary creation could be rewritten as a dictionary literal ”的解决方法

composer按装laravel

The solution to prompt "this list creation could be rewritten as a list literal" when adding elements to the list using the append() method in pychart

mysql json

Li Kou today's question 513 Find the value in the lower left corner of the tree

Shadertoy基础教学02、画笑脸

五年连续亏损42亿,蘑菇如何渡劫?

Abnova LiquidCell-负富集细胞分离和回收系统

Usage of API interface test ------ post