当前位置:网站首页>Detailed explanation of srl16e in xilinxffpga

Detailed explanation of srl16e in xilinxffpga

2022-06-23 08:48:00 【ZeroEDA】

FPGA The shift register is often used in the development process , The shift register is usually used to beat a signal , Make the timing meet our needs . One of the most common ways to shoot is in process Shift a signal in a procedure statement ( stay verilog It's in always Shift in the process ).XilinxFPGA A primitive provided in SRL6E, Can be maximized 16 Shift register of shift bit register . It should be noted that ,SRL16E Primitives may have slightly different forms in different devices , The following is the Artix-7 In a series of devices SRL16E The original language :

// SRL16E: 16-bit shift register LUT with clock enable operating

// on posedge of clock (Mapped to a SliceM LUT6)

// Artix-7

// Xilinx HDL Language Template, version 2020.1

SRL16E #(

.INIT(16'h0000) // Initial Value of Shift Register Initialize the register

) SRL16E_inst (

.Q(Q), // SRL data output Register output port

.A0(A0), // Select[0] input Four output bits select the control address

.A1(A1), // Select[1] input

.A2(A2), // Select[2] input

.A3(A3), // Select[3] input

.CE(CE), // Clock enable input Register enable port

.CLK(CLK), // Clock input Clock port

.D(D) // SRL data input Register input port

);example:

`timescale 1ns / 1ps

module SRL16E_Test(

input clk_in,

output wResetQ,

output wEnableN

);

wire wResetQ;

wire wEnableN;

SRL16E #( .INIT( 16'hFF00 ) ) mReset

( .CLK ( clk_in ),

.CE ( 1'b1 ),

.A0 ( 1'b1 ), .A1( 1'b1 ), .A2( 1'b1 ), .A3( 1'b1 ), // Select the first 16 An output

.D ( 1'b0 ),

.Q ( wResetQ ) );

SRL16E #( .INIT( 16'h000F ) ) mEnable

( .CLK ( clk_in ),

.CE ( 1'b1 ),

.A0 ( 1'b1 ), .A1( 1'b1 ), .A2( 1'b1 ), .A3( 1'b1 ), // Select the first 16 An output

.D ( 1'b1 ),

.Q ( wEnableN ) );

endmodule

Testbench:

`timescale 1ns / 1ps

module tb_SRL16E;

reg clk_in;

wire wResetQ;

wire wEnableN;

always #10 clk_in <= ~clk_in; // Clock signal 50M

initial begin

clk_in = 1'b1;

end

SRL16E_Test u_SRL16E(

.clk_in (clk_in ),

.wResetQ (wResetQ ),

.wEnableN (wEnableN )

);

endmodule

Waveform

边栏推荐

- 297. Serialize and Deserialize Binary Tree

- C # advanced learning -- virtual method

- Use newbeecoder UI implements data paging

- 鸿蒙读取资源文件

- Set interface and set sub implementation classes

- kernel log调试方法

- List interface three sub implementation classes

- 6月《中國數據庫行業分析報告》發布!智能風起,列存更生

- Dongyuhui, the "square face teacher", responded that the popularity was declining: do a good job of live broadcasting of agricultural products to benefit farmers and consider supporting education

- Leetcode topic analysis spiral matrix II

猜你喜欢

Basic use of check boxes and implementation of select all and invert selection functions

![[cloud computing] GFS ideological advantages and architecture](/img/98/2a4ef0ca805add24d431dac9808903.png)

[cloud computing] GFS ideological advantages and architecture

点云库pcl从入门到精通 第十章

Analysis of JMeter pressure measurement results

自组织映射神经网络(SOM)

Le rapport d'analyse de l'industrie chinoise des bases de données a été publié en juin. Le vent intelligent se lève, les colonnes se régénèrent

297. Serialize and Deserialize Binary Tree

6月《中国数据库行业分析报告》发布!智能风起,列存更生

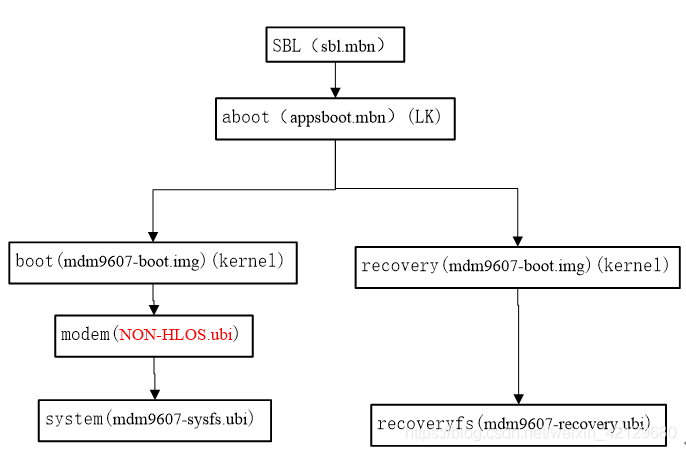

高通9x07两种启动模式

Why do we say that the data service API is the standard configuration of the data midrange?

随机推荐

Why is the easycvr Video Fusion platform offline when cascading with the Hikvision platform? How to solve it?

Chapter 1 open LDAP master-slave synchronization tower construction

5-旋转的小菊-旋转画布和定时器

Android kotlin coroutines KTX extension

Restore the default routing settings of the primary network card

[qnx hypervisor 2.2 user manual]6.2 network

Summary of communication mode and detailed explanation of I2C drive

给你的win10装一个wget

Interpretation of the most dirty technology in history, I can understand 60 it terms in seconds

You have a string of code, but do not support the lower version of go; Judge the go version number, you deserve it!

Object.defineProperty() 和 数据代理

USB peripheral driver - debug

Code quality level 3 - readable code

Third party payment in the second half: scuffle to symbiosis

Leetcode topic analysis count primes

Open source stealing malware mercurial found in the field for "educational purposes"

词性家族

[paper notes] catching both gray and black swans: open set supervised analog detection*

Go data types (II) overview of data types supported by go and Boolean types

Derivation and loading of the trained random forest model