当前位置:网站首页>Saying "Dharma" Today: the little "secret" of paramter and localparam

Saying "Dharma" Today: the little "secret" of paramter and localparam

2022-06-24 16:36:00 【FPGA technology Jianghu】

Today “ Law ”:paramter 、localparam Small “ Secret ”

Welcome to great Xia FPGA The new column of technology world said today “ Law ”, Of course , Here we are definitely not going to study and discuss the knowledge of laws and regulations , So what are we talking about , Here we are talking about some small details and methods in product development and technology learning , Welcome to study and exchange together , Good inspiration and essay , Welcome to contribute , Please indicate your pseudonym and related articles , Submission receiving email :[email protected] Today brings with it paramter 、localparam Small “ Secret ”, Don't talk much , Loading .

Today's talk “ Law ” Very brief , Because there's already a problem ahead Verilog HDL The basic grammar of learning content , Today, let's briefly review , I won't go into details , If you want to know more about it, you can have a look at it 《 One week to master FPGA Verilog HDL grammar 》.

stay Verilog HDL of use parameter To define constants , The box parameter To define an identifier to represent a constant , It's called a signed constant , A constant in the form of an identifier , Using an identifier to represent a constant can improve the readability and maintainability of the program .parameter Type data is a kind of constant data , The format of the description is as follows :

parameter Parameter name 1= expression , Parameter name 2= expression , …, Parameter name n= expression ;

That's right in most textbooks parameter Definition and use of , Parametric constants are often used to define delay times and variable widths .

parameter It can be used as an interface for passing parameters when instantiating the bottom module in the top module ,localparam The scope of is limited to the current module, Interfaces that cannot be passed as parameters .

But in Verilog in , This is a controversial issue , namely Parameter That is, as a constant , It is also a question of whether the use of parameters is reasonable and legal .

stay IEEE 2005 Before standard ,Verilog That's what it does . But constants don't just need secure encapsulation , It's also about intellectual property (IP), There are many questions about the indistinguishability of constant parameters .

With EDA Scale development ,IP Awareness enhancement , Constants need more security , therefore IEEE stay 2005 after , Join in localparam Reserved words , Used to define constants . Constants are used to define variables that are fixed in the current project and file . And parameters can be used as LPM The values exchanged , Be similar to C Formal parameters in languages .Verilog When the code model in is repeatedly referenced , Use LPM According to the needs of the site , Modify these parameters to customize . Obviously, constants don't need to be passed out , It doesn't need or allow to be customized on site .

stay 2005 edition Verilog Before , In the case that the constant parameters are not divided , Users of reusable code and designers of reusable code may not be the same person ( Or the team ), such , It's easy to create users with unknown internal details , Inadvertently modifying constants , Make the stable system go wrong , And feedback to the designer of the reused code . Another situation , Or worse ,IP Nuclear complexity and costs are increasing . Protect IP I'm getting more and more aware of it , And attack cracking IP People and teams are starting to emerge . This makes IP Authors have to protect their code , If a constant is passed as a parameter , It's a very important vulnerability , Of course, we have to add .

therefore , from now on , We're going to encapsulate the constants , Protect your code . adopt paramter 、localparam And other little “ Secret ”, We need to learn more .

Today “ Law ”, Take you to understand FPGA More secrets , Tips .

That's the end of the day , I wish you all the best , I'll see you again .

End

It will be updated continuously in the future , bring Vivado、 ISE、Quartus II 、candence Installation related design tutorial , Learning resources 、 Project resources 、 Good article recommendation and so on , I hope great Xia will continue to pay attention to .

The world is so big , Keep going , I wish you all the best , I'll see you again !

边栏推荐

- Heavy release! Tencent cloud ASW workflow, visual orchestration cloud service

- Tencent blue whale Zhiyun community version v6.0.3 was officially released together with the container management platform!

- 找出隐形资产--利用Hosts碰撞突破边界

- Global and Chinese market of inverted syrup 2022-2028: Research Report on technology, participants, trends, market size and share

- Kubernetes characteristic research: sidecar containers

- Tencent releases the full platform version of reasoning framework TNN, and supports mobile terminal, desktop terminal and server terminal at the same time

- How do HPE servers make RAID5 arrays? Teach you step by step today!

- B. Terry sequence (thinking + greed) codeforces round 665 (Div. 2)

- Istio FAQ: sidecar stop sequence

- Goby+awvs realize attack surface detection

猜你喜欢

Advanced programmers must know and master. This article explains in detail the principle of MySQL master-slave synchronization

C. K-th not divisible by n (Mathematics + thinking) codeforces round 640 (Div. 4)

B. Terry sequence (thinking + greed) codeforces round 665 (Div. 2)

A survey on dynamic neural networks for natural language processing, University of California

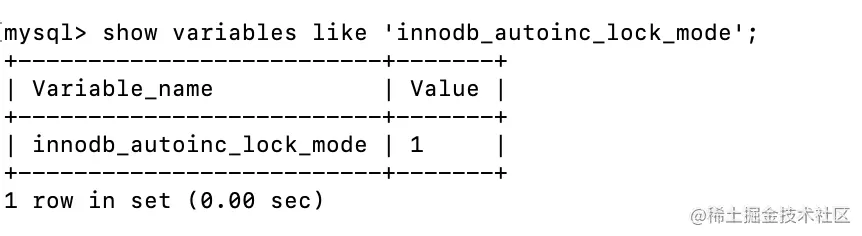

MySQL Advanced Series: Locks - Locks in InnoDB

ZOJ - 4104 sequence in the pocket

Ui- first lesson

C. Three displays(动态规划)Codeforces Round #485 (Div. 2)

![[go] concurrent programming channel](/img/6a/d62678467bbc6dfb6a50ae42bacc96.jpg)

[go] concurrent programming channel

A survey of training on graphs: taxonomy, methods, and Applications

随机推荐

Annual contribution! Tencent cloud middleware product upgrade conference is in hot registration!

AI video structured intelligent security platform easycvr intelligent security monitoring scheme for protecting community residents

Pytorch 转置卷积

The mystery of redis data migration capacity

ThinkPHP 漏洞利用工具

6 things all engineers should know before FEA

#夏日挑战赛# HarmonyOS - 实现带日期效果的待办事项

What is a server

PyTorch中的转置卷积详解

Ps\ai and other design software pondering notes

Embedded Software Engineer written interview guide arm system and architecture

TRTC web end imitation Tencent conference microphone mute detection

[go] runtime package for concurrent programming and its common methods

Problems encountered in the work of product manager

Serial of H3CNE experiment column - spanning tree STP configuration experiment

Some experiences of project K several operations in the global template

What is zero trust? Three classes will show you how to understand him!

Modern finite element analysis can easily achieve accurate results

Tencent blue whale container management platform was officially released!

CDs view permission check