当前位置:网站首页>FPGA的虚拟时钟如何使用?

FPGA的虚拟时钟如何使用?

2022-06-24 06:55:00 【碎碎思】

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟:

但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

首先,虚拟时钟用于什么地方?

虚拟时钟通常用于设定输入和输出的延时,即set_input_delay和set_output_delay。可能有同学忘记这两个约束的用法了,这里我们再展示一下:

set_input_delay 0.5 -clock clkA [get_ports A]

set_output_delay 1 -clock clkB [get_ports B]其中clkA和clkB就是我们使用create_clock创建的主时钟或者虚拟时钟。

主时钟在创建的时候需要指定时钟输入端口,虚拟时钟不需要指定端口,所以称之为虚拟时钟。那什么场景下要用到虚拟时钟呢?

外部IO的参考时钟并不是设计中的时钟

下图中,外部IO的参考时钟比设计中主时钟的路径上多了一个BUFFER,因此我们需要使用虚拟时钟来进行约束。

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virtclk -period 10

set_clock_latency -source 1 [get_clock virtclk]

set_input_delay -clock virtclk -max 4 [get_ports dina]

set_input_delay -clock virtclk -min 2 [get_ports dina]FPGA I/O路径参考时钟来源于内部衍生时钟,但与主时钟的频率关系并不是整数倍

如果I/O路径参考时钟源于内部的衍生时钟,那set_input_delay和set_output_delay约束中-clock参数后的时钟不能是衍生时钟,比如下图的例子中,输入10MHz时钟经过了MMCM后去采输入的数据。

a) 如果MMCM没有负的相移而且输出的频率也是10MHz,那么直接使用主时钟来约束input delay。

create_clock -period 100.000 -name clk [get_ports clk]

set_input_delay -clock clk -max 2.000 [get_ports datain]

set_input_delay -clock clk -min 1.000 [get_ports datain]b) 如果MMCM输出频率是60MHz,那么这个衍生时钟跟主时钟并不是整数倍关系,这时就需要用到虚拟时钟了

create_clock -period 100.000 -name clk [get_ports clk]

create_clock -name clk_port_vclk -period 16.67

set_input_delay -clock clk_port_vclk -max 2 [get_ports datain]

set_input_delay -clock clk_port_vclk -min 1 [get_ports datain]在不修改时钟特性的情况下针对I/O指定不同的jitter和latency

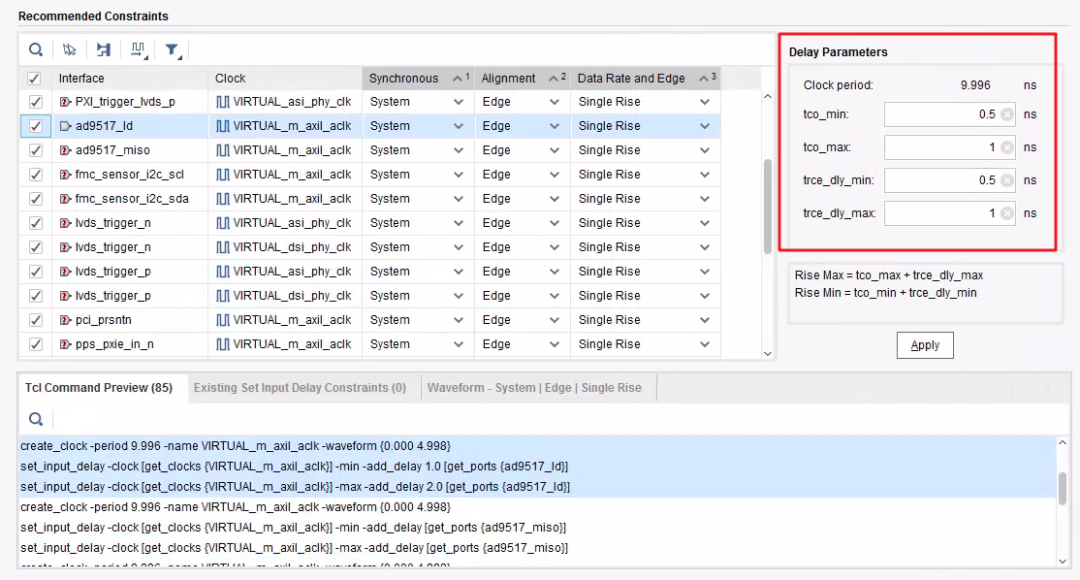

这个需求我们可以在Constraints Wizards中指定,简单又方便

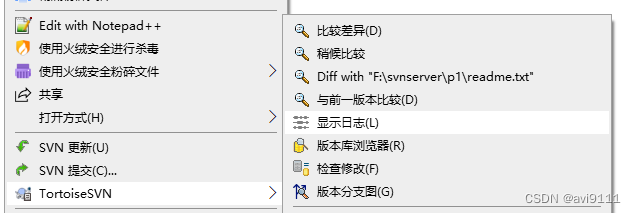

在设置完成后,可以看到Tcl Command Preview中提示的约束指令。

完

边栏推荐

- Case examples of corpus data processing (cases related to sentence retrieval)

- Part 1: building OpenGL environment

- 慕思股份在深交所上市:毛利率持续下滑,2022年一季度营销失利

- Mousse shares listed on Shenzhen Stock Exchange: gross profit margin continued to decline, and marketing failed in the first quarter of 2022

- Synchronous FIFO

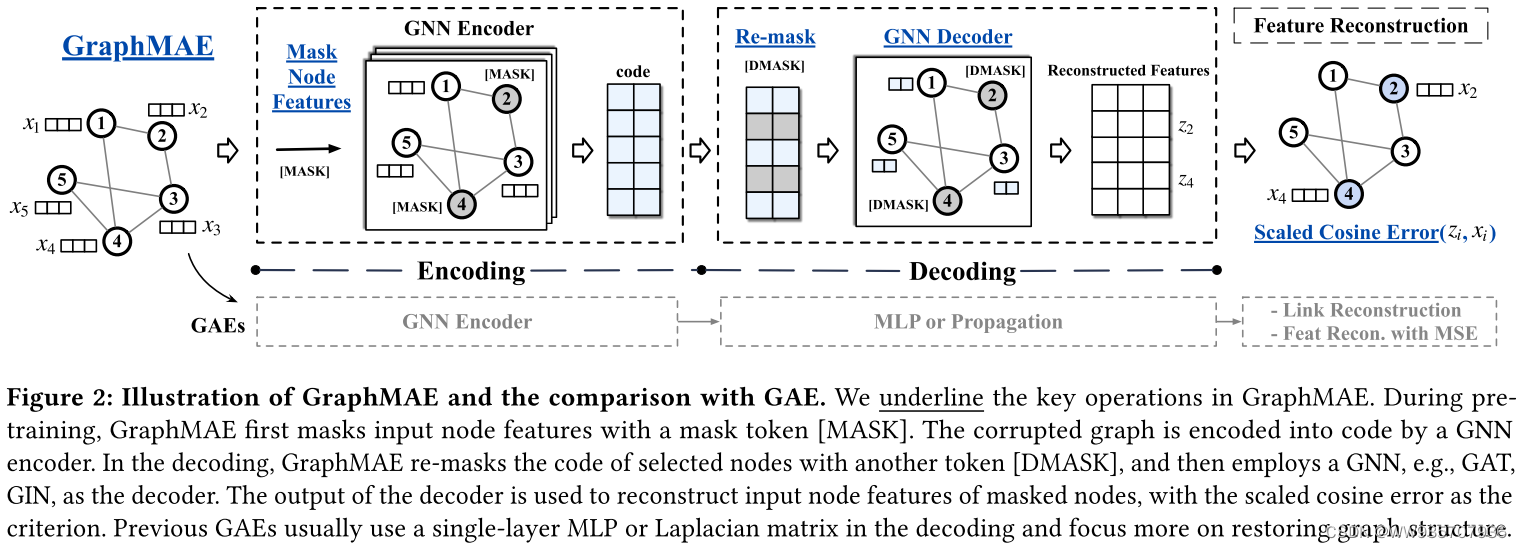

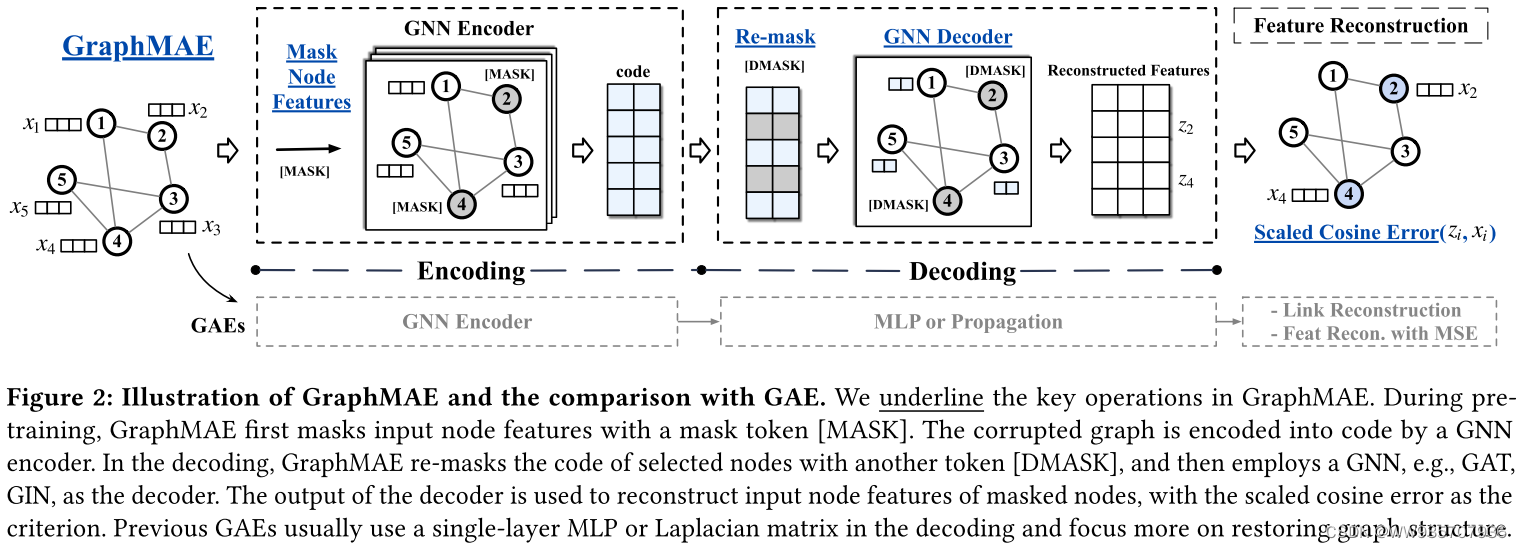

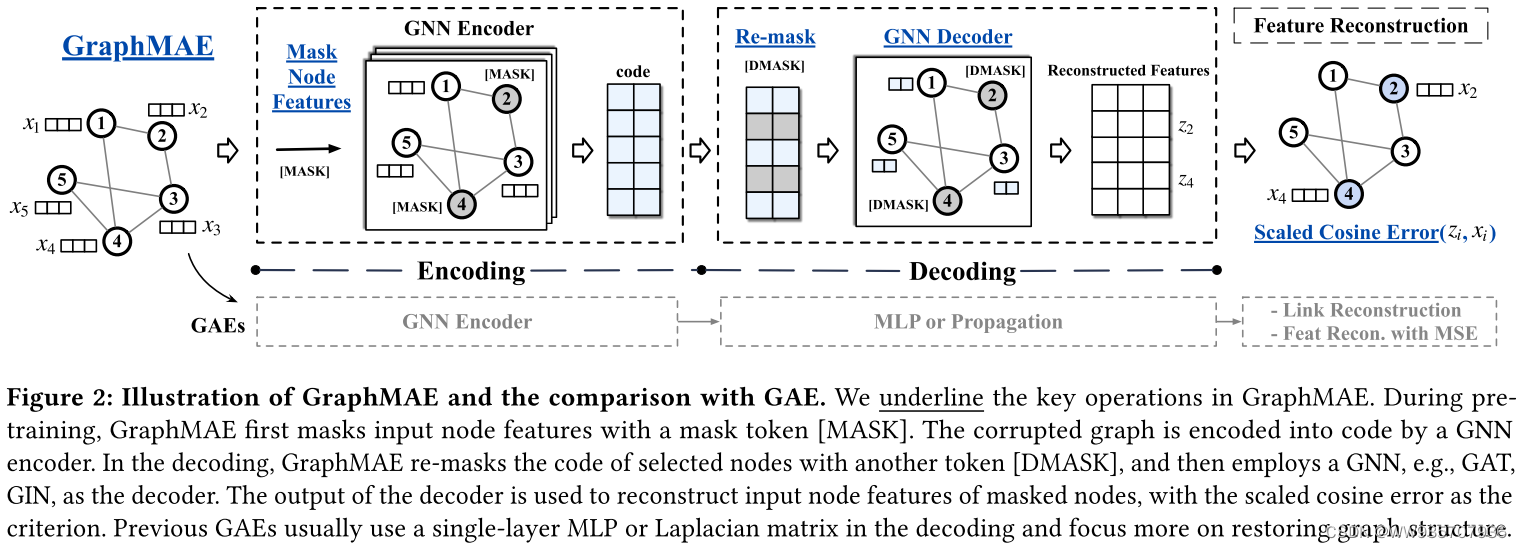

- Graphmae - - lecture rapide des documents

- [008] filter the table data row by row, jump out of the for cycle and skip this cycle VBA

- Echart's experience (I): about y axis yaxis attribute

- [teacher zhaoyuqiang] use the Oracle tracking file

- 毕业两年月薪36k,说难也不难吧

猜你喜欢

Swift Extension ChainLayout(UI的链式布局)(源码)

Vulnhub靶机:BOREDHACKERBLOG_ CLOUD AV

Graphmae - - lecture rapide des documents

GraphMAE----論文快速閱讀

Graphmae ---- quick reading of papers

Swift extension networkutil (network monitoring) (source code)

Part 2: drawing a window

第 2 篇:绘制一个窗口

Ad-gcl:advantageous graph augmentation to improve graph contractual learning

Svn actual measurement common operation record operation

随机推荐

Any remarks

Interview tutorial - multi thread knowledge sorting

Gossip: what happened to 3aC?

第 1 篇:搭建OpenGL环境

Common array encapsulation

[teacher zhaoyuqiang] use the Oracle tracking file

软件工程导论——第三章——需求分析

UTC、GMT、CST

Leetcode 207: course schedule (topological sorting determines whether the loop is formed)

【资料上新】迅为基于3568开发板的NPU开发资料全面升级

Graphmae - - lecture rapide des documents

Methods of vector operation and coordinate transformation

对于flex:1的详细解释,flex:1

慕思股份在深交所上市:毛利率持续下滑,2022年一季度营销失利

[test development] first knowledge of software testing

Introduction of model compression tool based on distiller

Jenkins 太老了 试试它?云原生 CI/CD Tekton

Chapitre 2: dessiner une fenêtre

Leetcode exercise - jumping game, combination summation

1-4metaploitable2 introduction