当前位置:网站首页>jvm-01. Instruction rearrangement

jvm-01. Instruction rearrangement

2022-06-23 05:56:00 【CaptainCats】

Command rearrangement

The execution of instructions 5 Stages

Almost all von Neumann computers CPU, The execution of an instruction can be divided into 5 Stages :

1、 Take command IF;

2、 Number of decoded and read accesses ( Read operands )ID;

3、 Execution instruction EX;

4、 Memory access ( The calculation results are loaded into memory )MEM;

5、 The result is written back to ( register )WB;

Each of these steps is handled by different hardware ,

The same steps need to wait for the hardware to idle before continuing , That is to say :

Two consecutive instructions need to consume at least 6 A clock unit .

A=B+C, You need to perform 4 An instruction

Java The code in :A=B+C, You need to perform 4 An instruction :

Instructions 1: load B To register R1 in ;

Instructions 2: load C To register R2 in ;

Instructions 3: take R1 And R2 Add up , calculated R3;

Instructions 4: take R3 Assign a value to A.

Instructions 1 And instructions 2 There is no dependency between , Execute in normal order ,

Instructions 3 Depending on the results of the first two instructions ,

Need to wait for instructions 1、2 Load all calculation results into memory (MEM) after , To execute (EX),

Instructions 4 Depending on instructions 3 Result , We also need to wait in a wrong place .

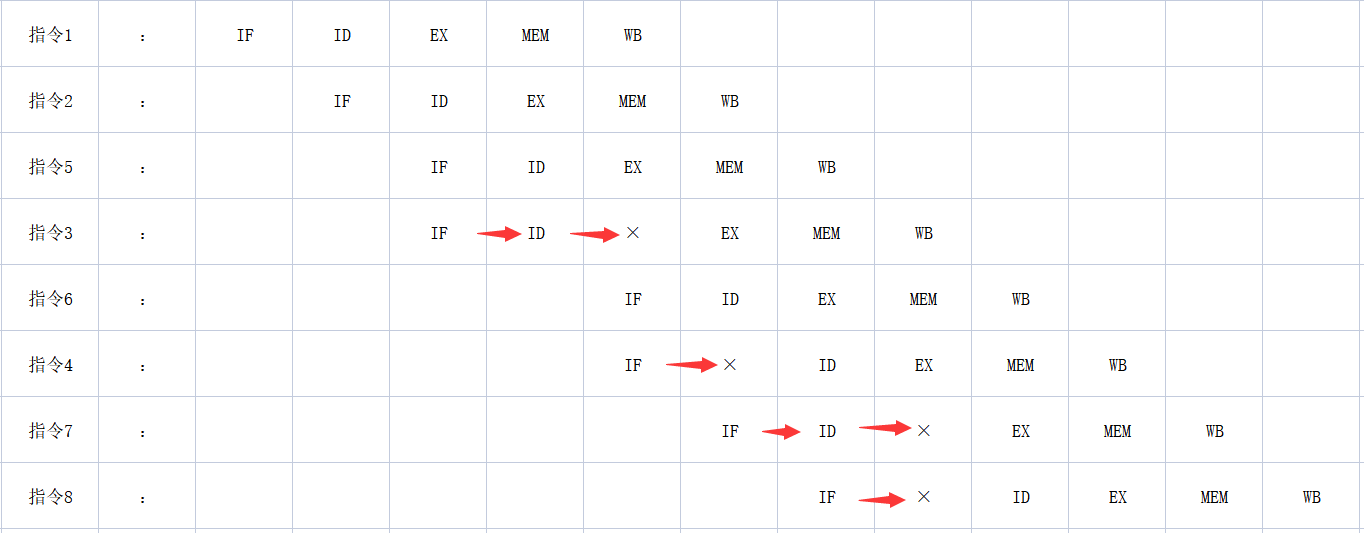

The red circle in the picture indicates that the hardware is idle due to waiting , Called bubbles ,

such 4 The clock unit length of an instruction is not ideal 8, It is 9.

A=B+C; D=E+F;

Take a more complicated example

A=B+C;

D=E+F;

Instructions 1: load B To register R1 in ;

Instructions 2: load C To register R2 in ;

Instructions 3: take R1 And R2 Add up , calculated R3;

Instructions 4: take R3 Assign a value to A.

Instructions 5: load E To register R4 in ;

Instructions 6: load F To register R5 in ;

Instructions 7: take R4 And R5 Add up , calculated R6;

Instructions 8: take R6 Assign a value to D.

This requires 14 A clock unit ,

Is there any way to eliminate these bubbles , Reduce the loss caused by idle hardware ,

The way is to put the instructions 5、6 Line up to the command 2 after ,

Then give the instructions 6 Line up to the command 3 after , Eliminate all bubbles , Make the most of your computer hardware ,

Command rearrangement

The clock unit length ranges from 14 Reduced to 12, This is the purpose of instruction rearrangement .

Disorderly execution

However, instruction rearrangement also brings the problem of out of order execution , If the sequence is out of order, the data will be inconsistent ,

Java How to ensure orderly execution under specific circumstances :jvm-02. Order guarantees .

Impropriety , Please correct .

Reference material :

The road is round :Java Memory model and instruction rearrangement

Technical tinkle : The meaning of instruction rearrangement

Let nature take its course ~: Detailed explanation of computer instruction execution process

边栏推荐

- [Stanford Jiwang cs144 project] lab2: tcpreceiver

- Leetcode topic analysis add binary

- Wechat applet: a new interesting test

- ssm项目搭建

- Alibaba cloud ack one and ACK cloud native AI suite have been newly released to meet the needs of the end of the computing era

- Opencv display image

- iNFTnews | 加密之家从宇宙寄来的明信片,你会收到哪一张?

- Excel sheet column title for leetcode Title Resolution

- Real MySQL interview question (23) -- pinduoduo ball game analysis

- Visdom draws multiple dynamic loss curves

猜你喜欢

True MySQL interview question (XXII) -- condition screening and grouping screening after table connection

Lottery DDD code

Kotlin Android simple activity jump, simple combination of handler and thread

MySQL面试真题(二十五)——常见的分组比较场景

Real MySQL interview questions (25) -- common group comparison scenarios

Dolphin scheduler dolphin scheduling upgrade code transformation -upgradedolphin scheduler

MySQL面试真题(二十二)——表连接后的条件筛选及分组筛选

Three most advanced certifications, two innovative technologies and two outstanding cases, Alibaba cloud appeared at the cloud native industry conference

Alibaba cloud object storage oss+picgo+typera implements the construction map

MySQL面试真题(二十一)——金融-贷款逾期

随机推荐

Skill self check | do you know these 6 skills if you want to be a test leader?

MySQL面试真题(二十八)——案例-通讯运营商指标分析

jvm-06.垃圾回收器

Wechat applet: wechat can also send flash photos to create wechat applet source code download and customize flash time

MySQL面试真题(二十七)——RFM分析法对用户进行分类

Real MySQL interview question (23) -- pinduoduo ball game analysis

Redis cache penetration solution - bloom filter

The construction of digital factory can be divided into three aspects

PAT 乙等 1012 C语言

A bit of knowledge - folding forging and Damascus steel

Kotlin Android simple activity jump, simple combination of handler and thread

【斯坦福计网CS144项目】Lab2: TCPReceiver

数字藏品如何赋能经济实体?

【数据库备份】通过定时任务完成MySQL数据库的备份

AHA C language Chapter 7 you can do more with it (talks 27-28)

Leetcode topic analysis add binary

The difference between SaaS software and traditional software delivery mode

PAT 乙等 1010 C语言

Wechat applet: production and generation of love guarantee

MySQL character set