当前位置:网站首页>Recognize the interruption of 80s51

Recognize the interruption of 80s51

2022-06-26 08:12:00 【Huawei SCM vision】

interrupt (interrupt) yes CPU When executing the program , An event that occurs to the system ( The program itself or external causes ) A reaction made , Temporarily put down the current program , Start by executing a specific program , After completing the specific procedure , Then return to execute the program just dropped . For example, the user presses a button , The program must process the user's button request in a timely manner , Then go back and continue .

such as , The teacher is giving a lecture , And the students have questions , You can raise your hand at any time , The teacher will immediately suspend his lecture , Help students solve their doubts , Continue the course that was suspended just now , Such an action is an interruption .

Interrupt source

Interrupt source ( Interrupt request source ): Able to CPU The part that issued the interrupt request .

8051 Provide 5 Interrupt service ( Interrupt source ): External interrupt (INT0、INT1), Timer interrupt / The counter is interrupted (TF0、TF1), Serial port interrupt UART(RI/TI).

8052 Provide 6 Interrupt service ( Interrupt source ), In addition to containing 8051 Provided 5 Interrupts , It also includes a third timer / Counter (Timer2) The interrupt .

MCS-51 The interrupt

> External interrupt

External interrupt INT0/INT1,CPU adopt 12 Pin ( namely P3.2) And 13 foot ( namely P3.3) To receive requests for external interrupts .

The sampling method of external interrupt signal can be divided into level trigger ( Low level trigger ) And edge trigger ( Negative edge triggers , The real-time clock signal is triggered when it changes from high to low ) Two kinds of .

To use level triggering , Need to put TCON In register IT0( or IT1) Set to 0, Then as long as P3.2 Pin ( or P3.3 Pin ) Low level , That is, it is regarded as an external interrupt demand .

To use edge triggering, you need to set TCON In register IT0( or IT1) Set to 1, You just need to P3.2 Pin ( or P3.3 Pin ) The signal changes from high level to low level , That is, it is regarded as an external interrupt demand .

These interrupt requirements will be reflected in IE0( or IE1) in , if IE The register of EX0( or EX1)=1, And EA=1,CPU Will enter the interrupted service .

As for the interrupt priority register (IP register ), It is just to arrange the sequence of service execution when multiple interrupts occur , If there is only one interrupt , It will not affect .

> Timer / The counter is interrupted

Timer / The Counter interrupt has TF0 and TF1 Two (8052 More than a :TF2). If it's a timer ,CPU The internal clock pulses will be counted , And propose an internal interrupt ; If it's a counter ,CPU The external pulses will be counted , And propose an internal interrupt . As for the input of external pulse , It is through T0 Pin ( namely 14 foot , That is to say P3.4) And T1 Pin ( namely 15 foot , That is to say P3.5)

> Serial port interrupt

Serial port interrupt (UART) Yes RI or TI Two ,CPU adopt RXD Pin ( namely 10 Pin , That is to say P3.0) And TXD Pin ( namely 11 foot , That is to say P3.1) Request to receive (RI) Interrupt demand or transmission (TI) Interrupt demand .

> Related registers

In front of [MCS-51 Interrupt system diagram ] in , We can set the interrupt enable register (IE register ) As a switch of interrupt function , Interrupt priority register (IP register ) It is a switch to judge the priority of each interrupt . But in fact ,IE register 、IP register 、TCON Every register is a 8 Bit addressable register , Here's the picture :

Interrupt priority

If not in IP Set priority in register , Then the priority of the interrupt is :INT0 >TF0>INT1>TF1>RI/TI.

If priority is set :

hypothesis TF1=1, Then the interrupt priority should be :TF1>INT0 >TF0>INT1> RI/TI;

hypothesis TF0 =1,INT1=1, Then the interrupt priority should be :TF0>INT1>INT0 > TF1>RI/TI.

Timer / Counter control register TCON in , Some settings are related to the sampling of external interrupt signals . among IT0 And IT1 Respectively INT0 And INT1 Sampling signal setting bit of :

If set to 1, The falling edge trigger signal is used ;

If set to 0, Is triggered by low level .

IE0 And IE1 By CPU Interrupt flag bit operated , When an interrupt occurs, it will be set to 1, At the end of the interrupt , Revert to 0.

Interrupt application

The interrupt setting includes turning on the interrupt switch (IE Register settings )、 Setting of interrupt priority (IP Register settings )、 Setting of interrupt signal (TCON Register settings ) etc. .

Set the interrupt command in the program :

IE=0x81 // namely 1000 0001, Compare with the front IE Register pictures are available EA=1,EX0=1, Enable INT0 interrupt

IE=0x84 // Enable INT1 interrupt

IE=0x85 // start-up INT0、INT1 interrupt

IP=0x04 // Set up INT1 Interrupts have the highest priority

TCON=0x8 // Set up INT1 Trigger with falling edge

Interrupt program format :void + Function name +interrupt + Numbers 0—4

0 External interrupt INT0

1 Timer / Counter TF0

2 External interrupt INT1

3 Timer / Counter TF1

4: Serial port TI/RI

Such as :void my_INT (void) interrupt 0

{

…….// Interrupt subroutine logic code

}

give an example :12 Pin ( namely P3.2) Access button , When the main program is running , Press this button , The program will enter the interrupt subroutine , Execute the logic of the subroutine , The interrupt subroutine is finished , Then enter the main program to continue execution .

The main program :

void main()

{

IE=0x81 // Enable INT0 interrupt

TCON=0x01 // Set up INT0 Trigger for falling edge

…..

While(1)

{

…….

}

}

void int0_test(void) interrupt0

{

……// Interrupt subroutine logic code

}

边栏推荐

- PyTorch-12 GAN、WGAN

- Solve psycopg2 NotSupportedError: PQconninfo not available in libpq < 9.3

- [NLP] vector retrieval model landing: Bottleneck and solution!

- 我想要股票账户优惠开户,如何操作?手机开户安全么?

- Wifi-802.11 2.4G band 5g band channel frequency allocation table

- Flume learning notes

- Handwritten instanceof underlying principle

- This article will take you to learn in detail what is FTTH

- Jz-063- median in data stream

- buuresevewp

猜你喜欢

OSPF design principles, commands take H3C as an example

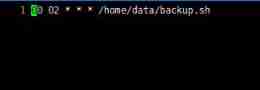

Automatic backup of MySQL database in the early morning with Linux

4 best practices for wireless (OTA) updates

Chapter 9 (using classes and objects)

Getting started with idea

How to define a digital factory and what is the relationship with smart factory and industry 4.0

Chapter VI (pointer)

Quickly upload data sets and other files to Google colab ------ solve the problem of slow uploading colab files

How to debug plug-ins using vs Code

buuresevewp

随机推荐

[untitled]

What are the characteristics of digital factory in construction industry

OSPF design principles, commands take H3C as an example

Solve psycopg2 NotSupportedError: PQconninfo not available in libpq < 9.3

项目管理学习

I want to open a stock account at a discount. How do I do it? Is it safe to open a mobile account?

Oracle 19C local listener configuration error - no listener

The difference between setstoragesync and setstorage

The 9th zero code training camp is officially open for registration! (Beijing, Shanghai, Guangzhou and Shenzhen)

D do not assign references to non domain parameters

Understanding of closures

Area of Blue Bridge Cup 2 circle

PyTorch-12 GAN、WGAN

Oracle database self study notes

What if the service in Nacos cannot be deleted?

Comparison version number [leetcode]

What is the difference between bone conduction earphones and ordinary earphones? Advantages of bone conduction earphones

Blue Bridge Cup 3 sequence summation

Pychart connects to Damon database

记一次开发 pgadmin 时执行 Building the Web Assets 遇到的依赖安装问题