当前位置:网站首页>[hdlbits questions] Verilog language (2) vectors

[hdlbits questions] Verilog language (2) vectors

2022-07-24 02:46:00 【Linest-5】

Catalog

Write it at the front

Arrived Verilog The vector part of grammar , This part is still relatively simple , So just give the title 、 Code and simulation results , I won't repeat anything else .

Vectors

Vector0

Build one with one 3 Bit input circuit , Then output the same vector , And split it into three separate 1 An output . Connect the output to the position of the input vector 0、 Location 1 etc. . In the chart , A scale line with a number next to it indicates a vector ( or “ Bus ”) Width , Instead of drawing a separate line for each bit in the vector .

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 ); // Module body starts after module declaration

assign outv = vec;

assign o2 = vec[2];

assign o1 = vec[1];

assign o0 = vec[0];

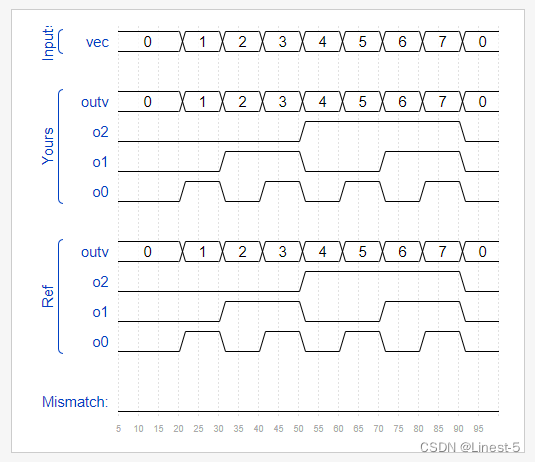

endmoduleSimulation waveform

Vector1

Vectorial Byte order ( Or informally called “ Direction ”) The index that is the least significant bit is lower ( Small end of the sequence , for example [3:0]) Or a higher index ( big-endian , for example [0:3]). stay Verilog in , Once a vector is declared in a specific byte order , You must always use it in the same way . for example , It is illegal to write in a statement . It is a good practice to be consistent with the byte order , Because if vectors with different byte order are allocated or used together , Strange mistakes will occur .

Build a combinational circuit , Half a word will be entered (16 position ,[15:0]) Split into lower [7:0] And higher [15:8] byte

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out_hi = in[15:8];

assign out_lo = in[7:0];

endmodule

Simulation waveform

Vector2

32 Bit vectors can be considered to contain 4 Bytes ( position [31:24]、[23:16] etc. ). Construct a circuit , The The circuit will reverse 4 Byte order of a byte word .

AaaaaaaaBbbbbbbbCcccccccDddddddd => DdddddddCcccccccBbbbbbbbAaaaaaaa

When the byte order of a piece of data needs to be exchanged , For example, at the small end x86 Systems and many Internet Between the big end formats used in the protocol , This operation is usually used .

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out[31:24] = in[7:0];

assign out[23:16] = in[15:8];

assign out[15:8] = in[23:16];

assign out[7:0] = in[31:24];

endmoduleSimulation waveform

Vectorgates

Build one with two 3 Bit input circuit , This input calculates the bitwise of two vectors OR、 The logic of two vectors OR And the inverse of two vectors (NOT). take The inverse function of is placed in The top half of ( Ascend the throne [5:3]), take The inverse function of is placed in the lower part .

module top_module(

input [2:0] a,

input [2:0] b,

output [2:0] out_or_bitwise,

output out_or_logical,

output [5:0] out_not

);

assign out_or_bitwise = a | b;

assign out_or_logical = a || b;

assign out_not[5:3] = ~b;

assign out_not[2:0] = ~a;

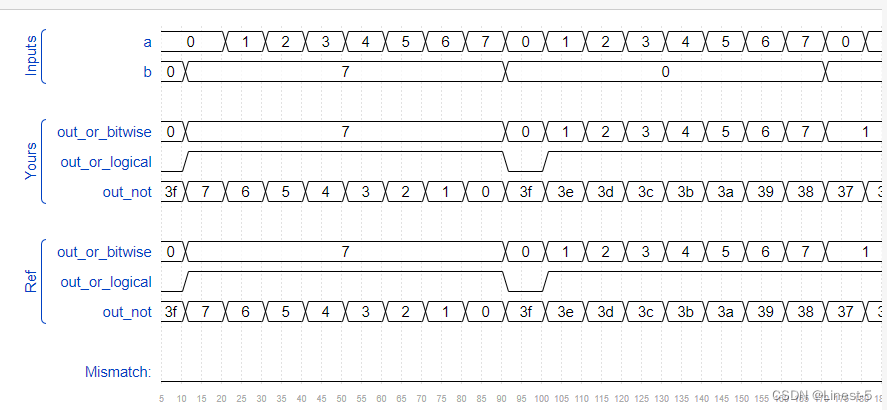

endmoduleSimulation waveform

Gates4

Build a combinational circuit with four inputs , stay [3:0] in .

Yes 3 Outputs :

- .out_and: Output 4 Channel input AND door .

- .out_or:4 Input OR Gate output .

- .out_xor: Output 4 Path input XOR gate .

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and = ∈

assign out_or = |in;

assign out_xor = ^in;

endmoduleWaveform simulation

Vector3

Bit mosaics

Given several input vectors , Connect them together , Then split them into multiple output vectors .

There are six 5 Bit input vector :a、b、c、d、e and f, in total 30 An input . There are four 8 Bit output vector :w、x、y and z, be used for 32 An output . The output should be a series of input vectors , Two heels 1 .

module top_module (

input [4:0] a, b, c, d, e, f,

output [7:0] w, x, y, z );

wire [31:0] combine;

assign combine = {a,b,c,d,e,f,{2'b11}};

assign w = combine[31:24];

assign x = combine[23:16];

assign y = combine[15:8];

assign z = combine[7:0];

endmoduleWaveform simulation

Vectorr

Given a 8 Bit input vector [7:0], Reverse its bit order .

module top_module(

input [7:0] in,

output [7:0] out

);

assign out = {in[0],in[1],in[2],in[3],in[4],in[5],in[6],in[7]};

endmoduleSimulation waveform

Vector4

Build a pair 8 Digital signature is extended to 32 Bit circuit .

This requires the symbol bit to be 24 Copies ( Copy bit [7]24 Time ) Connect , And then there was 8 Digit number itself .

module top_module (

input [7:0] in,

output [31:0] out );

assign out = {

{24{in[7]}},in};

endmodule

No simulated waveform

Vector5

Given five 1 Bit signal (a、b、c、d and e), Calculation 25 All in the bit output vector 25 Pairs 1 A bit more . If the two bits to be compared are equal , Then the output should be 1.

out[24] = ~a ^ a; // a == a, so out[24] is always 1.

out[23] = ~a ^ b;

out[22] = ~a ^ c;

...

out[ 1] = ~e ^ d;

out[ 0] = ~e ^ e;

- The top vector is for each input 5 Repeated series

- The bottom vector is 5 Input in series 5 A repetition

module top_module (

input a, b, c, d, e,

output [24:0] out );

assign out = {

{~{5{a}}^{a,b,c,d,e}},{~{5{b}}^{a,b,c,d,e}},

{~{5{c}}^{a,b,c,d,e}},{~{5{d}}^{a,b,c,d,e}},{~{5{e}}^{a,b,c,d,e}}};

endmoduleNo simulated waveform

边栏推荐

- Mysql database, sorting and single line processing functions

- Symbol類型

- 攻防世界WEB练习区(backup、cookie、disabled_button)

- Analyze the overall planning of steam and maker education classroom

- summernote支持自定义视频上传功能

- QT display Chinese garbled code

- 【HDLBits 刷题】Verilog Language(2)Vectors 部分

- Uie: unified model of information extraction

- SSM的技术论坛含前后台

- 动态规划-01背包问题

猜你喜欢

Attack and defense world web practice area (webshell, command_execution, simple_js)

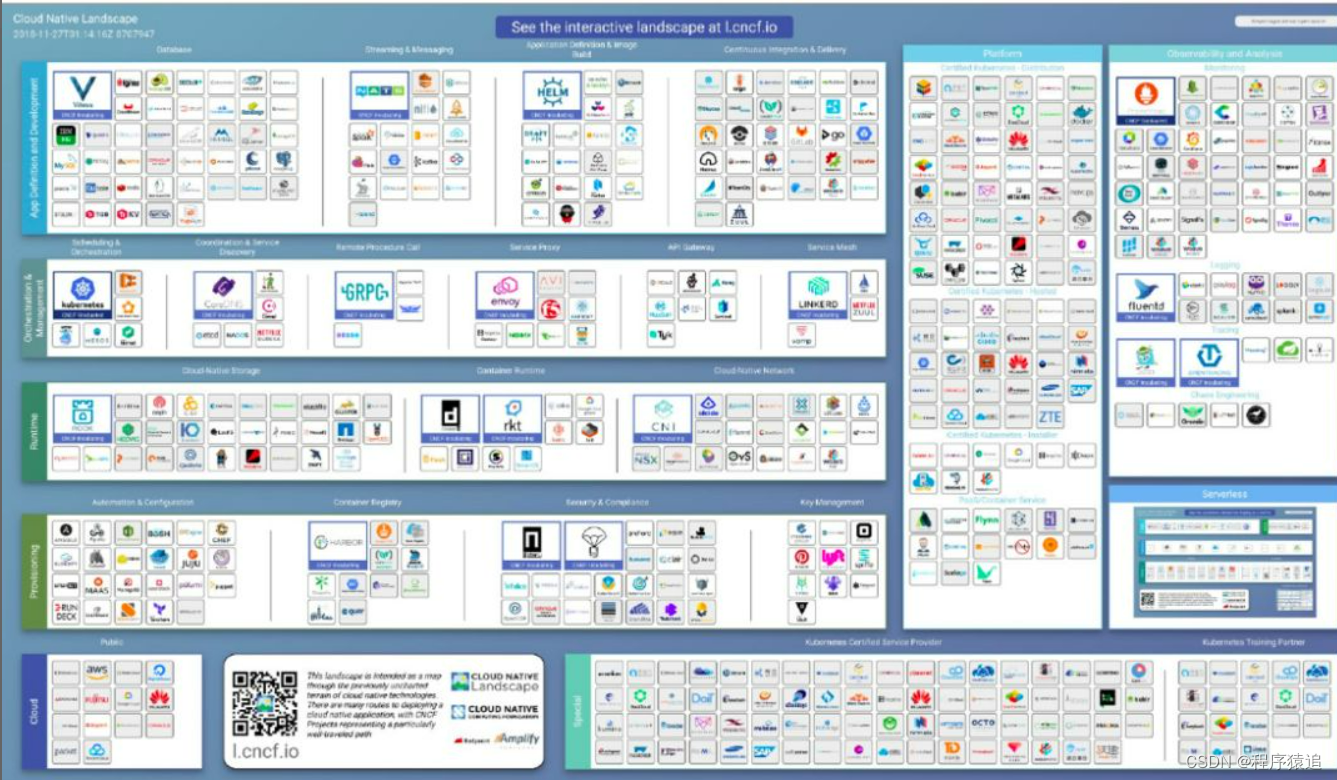

云原生讲解【扩展篇】

Causal learning open source project: from prediction to decision!

summernote富文本编辑器

动态规划-01背包问题

22 -- 二叉搜索树的范围和

![【补题日记】[2022牛客暑期多校1]I-Chiitoitsu](/img/be/47b8a86399f760e7cd6181528884c6.png)

【补题日记】[2022牛客暑期多校1]I-Chiitoitsu

508. The subtree element with the most occurrences and the pure C implementation of hash table method

TCP connection principle

Zone d'entraînement Web d'attaque et de défense (View source, get Post, robots)

随机推荐

Tutoriel sur l'utilisation de la ligne de temps unitaire

No coding is required, and the "asynchronous request reply" mode is automatically implemented

SSM family financial management personal financial management system accounting system

js傳參時傳入 string有數據;傳入 number時沒有數據;2[0]是對的!number類型數據可以取下標

自定义log注解,请求抓取

攻防世界WEB練習區(view_source、get_post、robots)

Unity TimeLine使用教程

Mysql数据库,分组函数篇

Attack and defense world web practice area (backup, cookie, disabled_button)

Mysql数据库,排序与单行处理函数篇

Custom log annotation, request fetching

[knowledge atlas] practice -- Practice of question and answer system based on medical knowledge atlas (Part2): Atlas data preparation and import

Unscramble the category and application principle of robot vision

redis数据类型概念

Detailed vector

[FPGA tutorial case 39] communication case 9 - interleaving deinterleaving data transmission based on FPGA

微信小程序实现折线面积图-玫瑰图-立体柱状图

[datasets] - downloading some datasets of flyingthings3d optical flow

compostion-api(setup中) watch使用细节

og seo