当前位置:网站首页>USB3.0: layout guide for vl817q7-c0

USB3.0: layout guide for vl817q7-c0

2022-07-23 19:28:00 【Q2185126449】

This article focuses on the common USB3.0 Hub driver chip via VL817-Q7C0 Of layout Layout treatment and precautions . It can be divided into three sections . This article focuses on the first section :PCB Key description of layout .

One :LATOUT Key notes of layout :

1: First of all PCB Impedance of board circuit , Here is an example of two-layer plate impedance precautions ,

<1> Double deck :

USB:90Ω+/- 10 % W-S-W → 11-5-11 mils

SATA: 100Ω+/- 10 % W-S-W →6-5-6 mils

<2>, The second is the spacing specification of the line

The distance between all impedance lines should be as large as possible , The ideal value is greater than 5 Times the line width (5W)

Impedance line and GND shape,VIA And the spacing of other parts should be greater than the width (3w), If you can 4 It is better to be above the line width .

The second is Diff pair When routing, you need to GND Copper foil space is also made

<3>.Vias on GND Routing shape

Close to the impedance line GND shape There should be a series of GND vias, also GND vias The distance between each other should be at least less than 200mils, And the smaller the spacing, the better .

notes : It should be avoided that precedents have bulges , Slender and without GND via Of GND shape.

2:90ohm Impedance line Via

Diff. Pair:W-S-W = 6-6-6 mils

Via spec.:drill = 12 mil,pad = 20 mil,antipad = 28 mil

Trace angle:45 degree

Generally, change the floor

Wrong line

3:Diff pari Routing settings

<1>Chip E-Pad

GND vias The more the better , And evenly distributed ( But be careful power plane The integrity of )

notes :GND Please don't lay copper + Word shop copper

4.:Power Plane

De-caps The closer you visit chip The better

All power supplies are better to use Acura power plane The design of the , And connected with other layers via The more, the better .

Power supply vias More than the backend ,Power The source of the .

5.:USB3.0 The connector

<1>USB 3.0 Std A, Stack A, and Std B Connectors

DIP Via for TX/RX pins:

<2>Miceo usb

TX/RX pads:

Pad Width = 20 mil

Etched GND width on L2 = 23 mil

<3>SMD Solder joint

That's all VL817 Of layout Layout description of , Due to limited space , Some details in the text are not explained carefully .

Section II PCBLAYOUT The inspection of And section III VLI Chip layout Layout description of It will be sorted out and released as soon as possible . For details of the first section, please contact the blogger , Talk about communication together .

边栏推荐

猜你喜欢

What is stack and the difference between stacks

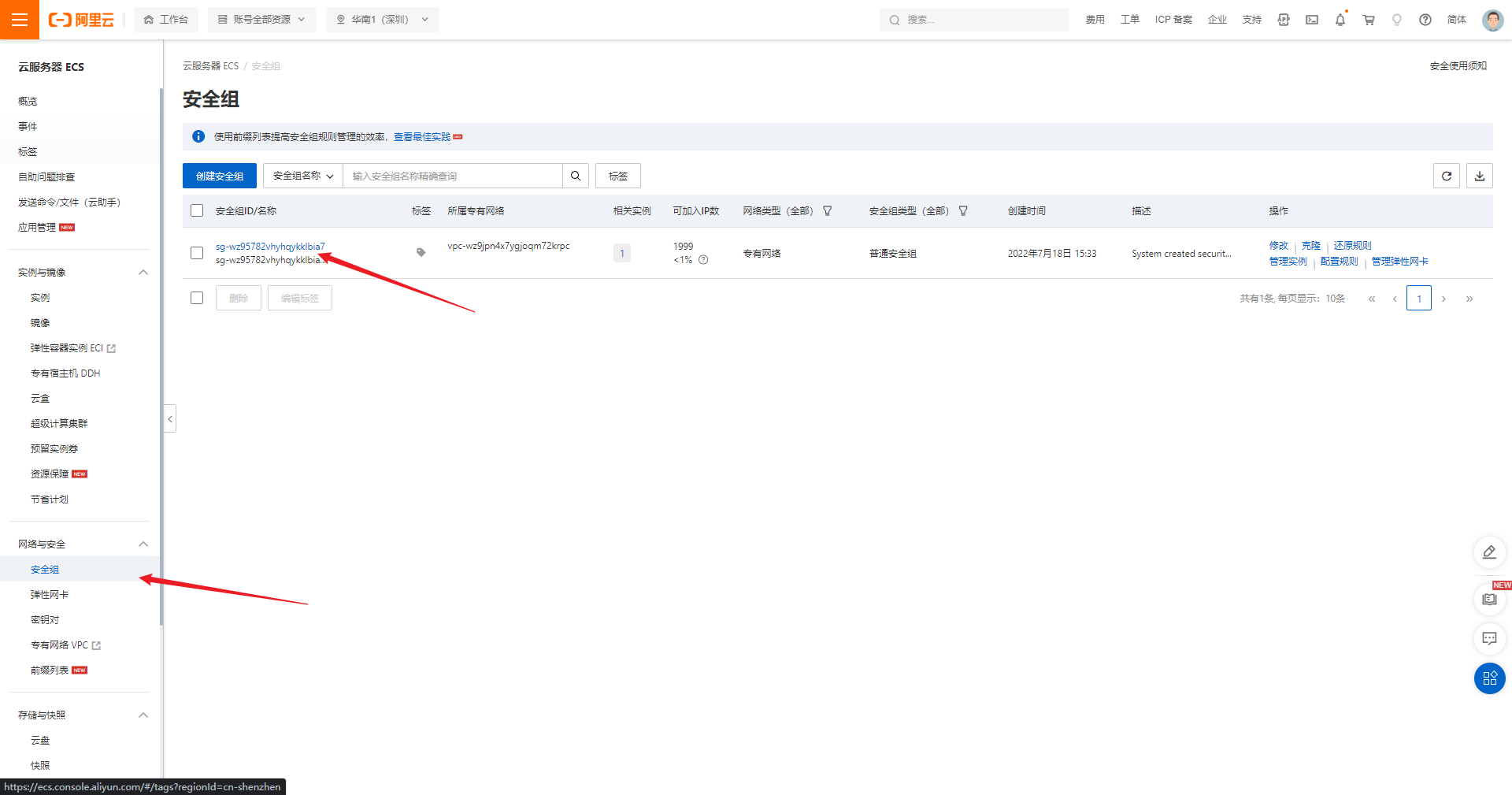

使用 frp 实现内网穿透

固态硬盘的工作原理揭秘

mBio | 海洋所孙超岷组在深海原位验证了微生物介导的单质硫形成新通路

软件测试岗位就业竞争压力大,985毕业的“打工人“同样存在苦不堪言

Digital security giant entrust revealed that it was attacked by blackmail software gangs in June

ES6其他语法及扩展语法总结

FPGA flash reading and writing based on SPI

Ros2 self study notes: rviz visualization tool

【leetcode天梯】链表 · 203 移除链表元素

随机推荐

ES6其他语法及扩展语法总结

@JPA annotation in entity

作为一名后台开发人员,你必须知道的两种过滤器

Learn and understand Architecture Design from business development

C language small project - address book (static version + dynamic version + file version)

小熊拍学习之LED灯的点亮

[Nuxt 3] (九)服务器路由

Challenges of decentralized storage

Implementation of IIC protocol with FPGA (I) IIC bus protocol

Emgucv common function function description "suggestions collection"

There is great competition pressure for software testing jobs, and the "migrant workers" who graduated from 985 also suffer

[shutter -- layout] linear layout (row and column)

去中心化存储面临的挑战

[machine learning] Wu Enda: lifelong learning

C语言小项目 -- 通讯录(静态版+动态版+文件版)

移动语义和完美转发浅析

C # startup program loses double quotation marks for parameters passed. How to solve it?

AE 教程,如何在 After Effects 中对 Illustrator 分图层文档进行动画绘制?

Fragment

MySQL数据库【数据库基础--引入篇】