当前位置:网站首页>【基础知识】~ 半加器 & 全加器

【基础知识】~ 半加器 & 全加器

2022-06-24 19:42:00 【AI很不错呦】

1. 半加器

1.1 定义

半加器,就是不考虑进位的加法器,只有两个输入和两个输出:输入A和B,输出和数sum和进位cout,半加器真值表如下:

1.2 关系表达式

1.3 电路设计

1.4 代码实现

module add_half(

input A ,

input B ,

output wire S ,

output wire C

);

assign S = A ^ B;

assign C = A & B;

endmodule

2. 全加器

2.1 定义

全加器就是在半加器的基础上引入一个进位输入,总共三个输入两个输出。全加器真值表如下:

2.2 关系表达式

这里的输出一共有两个,一个sum,一个进位cout。sum的值是A+B+cin然后去掉进位得到的,也就是说A、B、cin 中,如果输入1的个数是奇数,则sum为1,输入1的个数为偶数(含零)则sum为0。根据这个奇偶判定,可以想到用异或操作,所以得到表达式:

cout的值也好分析,cout是加和出来的进位,也就是说,如果A、B、cin三个数中,有两个及以上个1,则cout为1,这个容易得到表达式:

2.3 电路设计

2.4 代码实现

module add_full(

input A ,

input B ,

input Ci ,

output wire S ,

output wire Co

);

assign S = A ^ B ^ Ci;

assign Co = A&B | A&Ci | B&Ci;

endmodule

3. 两个半加器 实现 一个全加器

3.1 设计电路图

3.2 代码实现

`timescale 1ns/1ns

module add_half(

input A ,

input B ,

output wire S ,

output wire C

);

assign S = A ^ B;

assign C = A & B;

endmodule

/***************************************************************/

module add_full(

input A ,

input B ,

input Ci ,

output wire S ,

output wire Co

);

wire [1:0] s, c;

add_half m1 (

.A(A),

.B(B),

.S(s[0]),

.C(c[0]));

add_half m2 (

.A(s[0]),

.B(Ci),

.S(s[1]),

.C(c[1]));

assign S = s[1];

assign Co = c[0] | c[1];

endmodule

其实这是一道公司笔试题目,大家可以点击这里

参考文献

边栏推荐

- 【武汉大学】考研初试复试资料分享

- Docker installation redis- simple without pit

- shopee开店入驻流水如何提交?

- Do you need to improve your code reading ability? It's a trick

- 03_ Spingboot core profile

- Research Report on solar battery charger industry - market status analysis and development prospect forecast

- Servlet

- Push markdown format information to the nailing robot

- 京东618会议平板排行榜公布,新锐黑马品牌会参谋角逐前三名,向国货老大华为学习

- [laravel series 7.9] test

猜你喜欢

01_ Getting started with the spingboot framework

vulnhub DC: 2

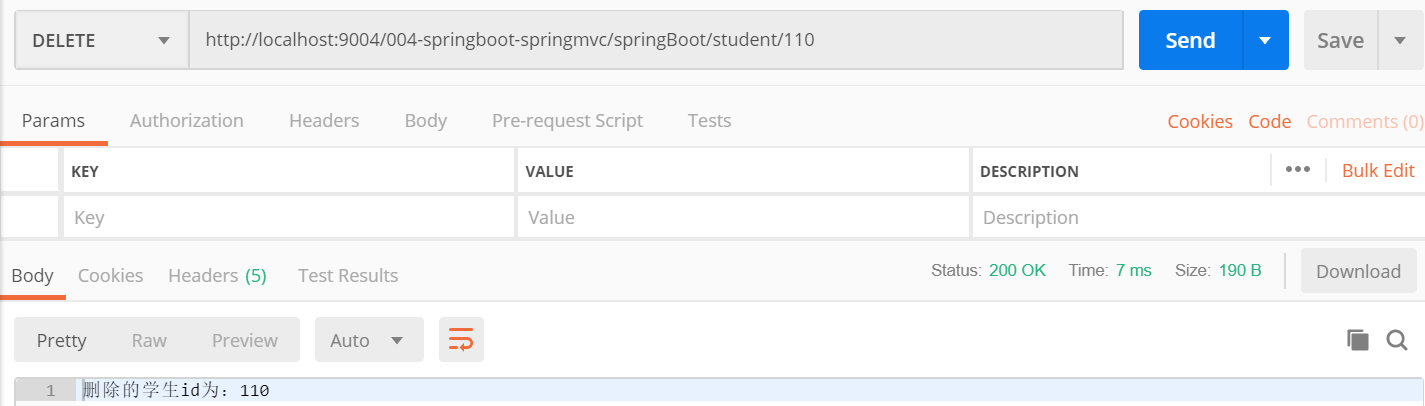

07_ Springboot for restful style

Push markdown format information to the nailing robot

Recommended movies: Northeast tiger, licorice pizza

15 lines of code using mathematical formulas in wangeditor V5

![[postgraduate entrance examination English] prepare for 2023, learn list9 words](/img/2d/9ff691c9ff50fba2df73f726db26f2.jpg)

[postgraduate entrance examination English] prepare for 2023, learn list9 words

![[ROS play with turtle turtle]](/img/94/4d1063f063d115aeef5cdf099278f8.png)

[ROS play with turtle turtle]

2022 safety officer-a certificate examination questions and answers

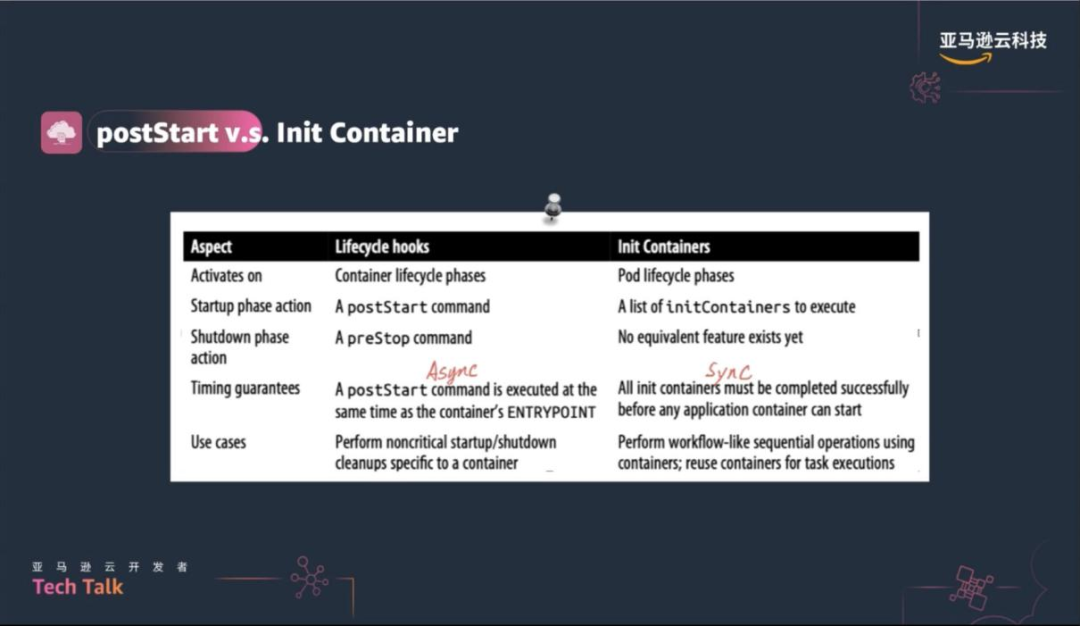

Tech talk activity review kubernetes skills of cloud native Devops

随机推荐

Financial management [3]

Win10 or win11 printer cannot print

vulnhub DC: 2

Do you need to improve your code reading ability? It's a trick

[text data mining] Chinese named entity recognition: HMM model +bilstm_ CRF model (pytoch) [research and experimental analysis]

Second IPO of Huafang group: grown up in Zanthoxylum bungeanum, trapped in Zanthoxylum bungeanum

Recommended movies: Northeast tiger, licorice pizza

【WSL】SSH 远程连接及宿主机端口转发配置

Are you afraid of being asked MySQL related questions during the interview? This 30000 word essence summary + 100 interview questions, and it's enough to hang the interviewer

[laravel series 7.9] test

What kind of processor architecture is ARM architecture?

MySQL kills 10 people. How many questions can you hold on to?

Simulated 100 questions and online simulated examination of high voltage electrician examination in 2022

京东618会议平板排行榜公布,新锐黑马品牌会参谋角逐前三名,向国货老大华为学习

Epics record reference 2 -- epics process database concept

力扣解法汇总515-在每个树行中找最大值

2022年高压电工考试模拟100题及在线模拟考试

Memory alignment of structures

Docker installation redis- simple without pit

It's hard to hear C language? Why don't you take a look at my article (7) input and output