当前位置:网站首页>Embedded hardware development tutorial -- Xilinx vivado HLS case (process description)

Embedded hardware development tutorial -- Xilinx vivado HLS case (process description)

2022-06-24 01:52:00 【Tranlong123】

front said

This paper mainly introduces HLS How to use the case , Applicable development environment :Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx SDK 2017.4.

Xilinx Vivado HLS(High-Level Synthesis, High level synthesis ) Tool support will C、C++ And so on , At the same time, support based on OpenCL And so on Xilinx Programmable logic device development , It can accelerate the process of algorithm development , Shorten time to market .

This case uses the technology of chuanglong TLZ7x-EasyEVM-S Development board , It is based on Xilinx Zynq-7000 series XC7Z010/XC7Z020 Heterogeneous multi-core processor with high performance and low power consumption SoC Evaluation board , Processor Integration PS End binuclear ARM Cortex-A9 + PL End Artix-7 framework 28nm Programmable logic resources , The evaluation board is composed of core board and evaluation bottom board . The core board has been professionally PCB Layout And high and low temperature tests to verify , Stable and reliable , It can meet various industrial application environments .

TLZ7x-EasyEVM-S Evaluation board

TLZ7x-EasyEVM-S Evaluation board evaluation board interface resources are rich , Leading out Gigabit Ethernet port 、 dual CAMERA、USB、Micro SD、CAN、UART Such as the interface , Support LCD Display expansion and Qt GUI development , It is convenient for rapid product scheme evaluation and technical pre research .

HLS The basic development process is as follows :

- HLS The project is newly built / Project import

- Compilation and simulation

- comprehensive

- IP Nuclear packaging

- IP Nuclear testing

HLS The case catalogue is described in detail in the following table .

surface 1

Catalog | Catalog | file / Catalog | explain |

|---|---|---|---|

hls_ip_demo | bin or hw/bin | xxx_xc7z010.bin/xxx_xc7z010.bit | xc7z010 PL End IP Nuclear test executable |

xxx_xc7z020.bin/xxx_xc7z020.bit | xc7z020 PL End IP Nuclear test executable | ||

project or hw/project | xxx_xc7z010 | xc7z010 PL End IP Nuclear testing Vivado engineering | |

xxx_xc7z020 | xc7z020 PL End IP Nuclear testing Vivado engineering | ||

sw | bin | PS End IP Core test bare metal executable | |

project | PS End IP Nuclear testing bare metal engineering | ||

vivado_hls | ip_package | xxx.zip | IP nucleus |

project | solution | Simulation scheme | |

src | HLS Engineering source | ||

test_bench | HLS Engineering simulation program or test file | ||

vivado_hls.app | HLS Engineering documents |

HLS For detailed development instructions, please refer to the following documents .

- ug871-vivado-high-level-synthesis-tutorial.pdf

- ug902-vivado-high-level-synthesis.pdf

HLS Development process description

This chapter is based on product data “4- Software data \Demo\FPGA-HLS-demos\” In the catalog led_flash Take the case as an example , demonstration HLS Development process . The function of this case is by PL End control evaluation backplane LED2 Flashing .

Before that , Please copy the corresponding case directory to Windows In the non Chinese path .

remarks :Windows The path has a length limit , Too long path will lead to an error in opening the project .

Before doing the following in this article , Please install the debugging tool according to the debugging document Xilinx Vivado Development kit . By default, this article uses the TL-DLC10 Downloader for operation demonstration .

HLS Project import

Double click the following icon on the desktop to open Xilinx Vivado HLS 2017.4, And click... In the pop-up interface “Open Project” Choose a case “vivado_hls\project\” Catalog , And then click “ determine ” Import HLS engineering .

chart 1

chart 2

chart 3

You can also build HLS engineering , And use C/C++ And so on .

Compilation and simulation

The emulator is located in Test Bench Under the table of contents , Used to verify Source In the catalog HLS Engineering source .

Import HLS After the project , Click on (Run C Simulation) Compile and simulate .

chart 4

The following interface will pop up , Check “Launch Debugger”, And click the OK.

chart 5

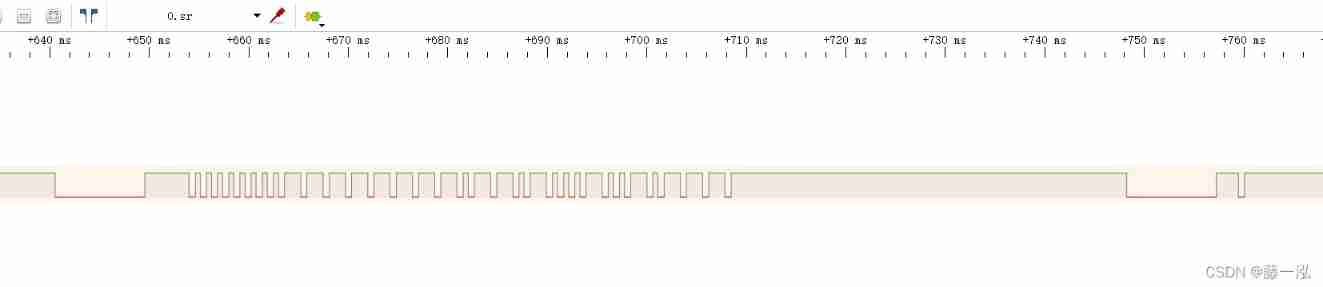

After compilation , It can run at full speed or in one step .

chart 6

comprehensive

This section demonstrates C/C++ And so on RTL Design , And generate a comprehensive report .

Click the upper right corner of the interface Synthesis Back to the engineering interface , Then click to start synthesis .

chart 7

chart 8

After the integration , The report file will open automatically .

chart 9

Through the report file, we can see the design time delay 、 Information such as resource occupancy .

chart 10

IP Nuclear packaging

After the integration , Click generation IP nucleus .

chart 11

chart 12

chart 13

After completion of operation , It will be in the case “vivado_hls\project\solution1\impl\ip\” Generate under directory IP nucleus .

chart 14

chart 15

IP Nuclear testing

Enter the case “hls_ip_demo\project\” or “hls_ip_demo\hw\project\” Corresponding platform PL End IP Nuclear testing Vivado Project directory , double-click .xpr File open project , The project has added to be tested by default IP nucleus .

chart 16

To import IP nucleus , Please refer to the following steps .

- Please click on “IP Catalog -> User Repository -> Add IP to Repository…”, Select... In the pop-up interface IP Click after checking OK.

chart 17

chart 18

- Right click “User Repository” Then click “Refresh Repository”, You can see the added IP nucleus .

chart 19

chart 20

- To add Vivado Self contained IP nucleus , Click on “Open Block Design”, Click... In the pop-up interface , And choose what you want IP The nuclear power will lead it into Engineering .

chart 21

chart 22

Click on Vivado On the left side of the interface “Generate Bitstream” Options , Click... In the pop-up interface OK Conduct PL End IP Nuclear testing Vivado Engineering compilation .

chart 23

chart 24

After compilation , Will be in Engineering “led_flash.runs\impl_1\” Generate under directory .bit and .bin Format executable .

chart 25

Reference resources PL End case development manual description loading PL End .bit Format executable , You can see the evaluation of the floor LED2 Flashing .

边栏推荐

- [tcapulusdb knowledge base] common problems of tcapulusdb local deployment

- Application of "popular science" UAV and video technology in fire scene

- LeetCode 1289. Descent path min and II

- Login server in VNC mode

- Tcapulusdb pays high tribute to Chinese journalists!

- [combat power upgrade] Tencent cloud's first arm architecture instance was launched! Experience the new architecture computing power!

- How to do AI speech synthesis? How to download the voice of AI speech synthesis?

- Tencent cloud Weibo was selected into the analysis report on the status quo of China's low code platform market in 2021 by Forrester, an international authoritative research institution

- [new function!] How anycast CLB supports multi location & dynamically accelerated load balancing services and high-speed Internet forwarding!

- Based on ARM embedded real-time streaming media service development and deployment, easygbs supports arm64 architecture

猜你喜欢

![[SQL injection 12] user agent injection foundation and Practice (based on burpsuite tool and sqli labs LESS18 target machine platform)](/img/c8/f6c2a62b8ab8fa88bd2b3d8f35f592.jpg)

[SQL injection 12] user agent injection foundation and Practice (based on burpsuite tool and sqli labs LESS18 target machine platform)

Stm32g474 infrared receiving based on irtim peripherals

![[SQL injection 13] referer injection foundation and Practice (based on burpseuite tool and sqli labs less19 target platform)](/img/b5/a8c4bbaf868dd20b7dc9449d2a4378.jpg)

[SQL injection 13] referer injection foundation and Practice (based on burpseuite tool and sqli labs less19 target platform)

I, a 27 year old female programmer, feel that life is meaningless, not counting the accumulation fund deposit of 430000

layer 3 switch

Review of AI hotspots this week: the Gan compression method consumes less than 1/9 of the computing power, and the open source generator turns your photos into hand drawn photos

It's too difficult for me. Ali has had 7 rounds of interviews (5 years of experience and won the offer of P7 post)

随机推荐

Oracle sqlldr quick import and sqluldr2 quick export

8、 Pipeline pipeline construction project

How to use voice synthesis? Can voice synthesis modify the voice?

[seckill] new / old users lock in the "explosive seckill zone" and snap up the one-year validity cloud function resource yyds for 63 yuan!

Cost composition and calculation method of system software

How do users of Fortress computers add servers? How much does it cost to add servers for fortress users?

Why promote steam education?

What does fortress server mean? What are the benefits of Fortress server installation

Gin framework: implementing distributed log tracing

2021-11-14:Fizz Buzz。 I'll give you an integer n and find the number from 1 to n

Make standardized tools in the cloud native era to realize efficient cloud R & D workflow

How to use the speech synthesis assistant? Does speech synthesis cost money?

[tcapulusdb knowledge base] how does tcapulusdb add a business cluster cluster?

Summary of various situations in which easycvr cannot use voice intercom function

Query report of each mic quality inspection result on SAP QM inspection lot?

Tcapulusdb Jun · industry news collection

Practical case - Tencent security hosting service MSS helped "zero accident" during the period of digital Guangdong re insurance!

Why use CDN content distribution network?

Software cost evaluation: a method for estimating software scale by fast function point method

[technical grass planting] how to batch check your server status? Cloud probe panel setup tutorial