当前位置:网站首页>White paper - Intel and Ashling, a well-known risc-v tool provider, strive to expand multi platform risc-v support

White paper - Intel and Ashling, a well-known risc-v tool provider, strive to expand multi platform risc-v support

2022-06-23 13:44:00 【Intel edge computing community】

Executive summary

Just FPGA for , One or more soft core processors may be instantiated in the programmable logic of the device , So that designers can integrate the programmable microcontroller and / Or a microprocessor core added to your design .

Now? , be based on FPGA The performance of soft core processors is becoming more and more important in the embedded market . Embedded applications running complex workloads in industrial and military markets need high-performance soft core processors that can be equipped with a variety of easy-to-use tools to accelerate software development .

RISC-V It can not only meet the performance requirements of these markets , It can also provide a continuous implementation technology module or intellectual property module (IP modular ) upgrade 、 Ways to continuously acquire advanced tools . In the process of development RISC-V The ecosystem also brings a wide range of software compatibility 、 Better tools and compiler support , And standard debugging environment .

By integrating intel FPGA The soft core processors used in migrate to open standards , And with well-known RISC-V Solution providers Ashling cooperation , Intel gives users access to modern integrated development environments (IDE)、 compiler 、 Support for a diverse ecosystem of debuggers and operating systems .

Intel RISC-V Strategy

Intel is a pioneer in the microprocessor industry . As early as 50 Years ago 1971 In, it created the first commercial microprocessor Intel 4004.1978 year , Intel created x86 framework , This is the early instruction set architecture for microprocessor-based computing (ISA) One of . Now? ,x86 Instruction set architecture has developed into a widely used architecture for general computing applications in the world . since x86 Since the advent of the instruction set architecture , Intel will 40 I have spent many years developing a successful instruction set architecture 、 Build fruitful partnerships and develop high productivity ecosystems , These industries are obvious to all .

In addition to microprocessor products , Intel's programmable Solutions Division has also developed large capacity and high performance FPGA. These devices provide users with a variety of options , Including configurable embedded SRAM、 High speed transceiver 、 High speed input / Output (I/O)、 Logical blocks and routes . Built in IP Modules combined with excellent software tools , Effectively shorten FPGA Development time 、 Reduced power consumption and cost .

2022 year 2 month , Intel becomes the global open hardware standards organization RISC-V International Active members of . Open RISC-V Ecosystems provide an indispensable open platform for modern computing 、 Modular building foundation . Join in RISC-V after , Intel shows its leadership , A number of activities have been carried out , Expanded... For all industry stakeholders RISC-V The potential of ecosystems .

be based on RISC-V Strategy , Intel and RISC-V The major partners in the ecosystem work together , These partners include Ashling、 Jingxin Technology 、Esperanto Technologies、SiFive and Ventana Micro Systems.

Intel plans to invest several funds , To strengthen RISC-V Build ecosystems and help drive RISC-V Further landing . Under the organization of Intel , These investments will help those who

■ Technology Collaborative Optimization

■ Preferred wafer sharing service

■ Support customer design

■ Build a development board

Continuously develop software infrastructure

for example , Intel plans to offer a range of proven RISC-V The kernel of , The performance of these cores has been optimized for different market segments . Intel will cooperate with major suppliers , Optimize for Intel process IP modular , In order to ensure that RISC-V It can be used in various kernel types from embedded kernel to high-performance kernel The chip works well .RISC-V The product will be available in three types :

■ Based on Intel Technology manufacturing partner products .

■ Gain differentiation IP Module licensed RISC-V kernel .

■ Intel Advanced Packaging Technology and high-speed chip to chip interface RISC-V Small chip building blocks .

Intel is right RISC-V The investment of , Plus RISC-V Community support , Will accelerate open RISC-V The development process of modules and other deliverables . Besides , Intel foundry services (IFS) The Department will also sponsor an open source software development platform . The platform supports free experiments , The ecological system 、 Both universities and alliance partners can benefit from it . This OEM service strategy will provide a wide range of technologies for Intel process optimization . Intel foundry services can provide services for x86、Arm and RISC-V All three major industries' mainstream instruction set architecture optimization technologies . and , Intel has seen more support from OEM customers RISC-V IP Strong demand for modular products .

Intel eASIC equipment :

from FPGA To ASIC Shortcut

In order to adapt to various business and development modes , Intel also offers advanced intel eASIC Equipment and ASIC Choose a plan . Intel eASIC The device is structured ASIC, This is a way between FPGA And standard units ASIC The intermediate technology between the two . And the standard unit ASIC You can use Intel foundry services to create . This service is a completely vertical independent OEM business , Designed to help meet the growing global demand for semiconductors .

Intel eASIC The equipment performance is between FPGA and ASIC Between realizations . Use Intel eASIC equipment , It can keep up with FPGA Achieve the same dominant frequency , It can also reduce power consumption , Can also maintain heat dissipation / Improve performance while maintaining the same power budget . With standard units ASIC comparison , Intel eASIC Time to market (TTM) faster , One time cost input (NRE) A lower . by comparison , Standard unit ASIC It can provide higher performance with lower power consumption . Once a design of Intel FPGA The implementation is verified , The design can be solidified into Intel with lower cost and power consumption eASIC Equipment or higher performance 、 Power consumption is further reduced ASIC. Developers may also learn from the design of Intel FPGA Implementation begins , Then migrate to Intel eASIC equipment , Then migrate to the complete ASIC( chart 1).

chart 1. Intel offers from FPGA To Intel eASIC Equipment and ASIC Migration path for , To reduce costs 、 Reduce power consumption 、 Lifting performance .

Intel RISC-V The policy supports both Intel based FPGA Development RISC-V, It also supports subsequent deployment to Intel FPGA、 Intel eASIC Equipment and ASIC( Including those provided by Intel wafer foundry services ASIC). Besides intel , It is difficult for other companies to provide services from FPGA To Intel eASIC The equipment goes to ASIC These can reduce costs 、 Reduce power consumption 、 Migration path to improve performance .

RISC-V about FPGA Customer value

RISC-V Is an open source hardware instruction set architecture , Began in 2010 year . Unlike most other instruction set architectures ,RISC-V It is provided under the open source license .RISC-V The instruction set specification defines 32 Bit and 64 Bit addressing space variant . Instruction set has the characteristics of variable width and extensibility , Designed to address a wide range of use cases .

In addition to the open source instruction set architecture ,RISC-V Its success can also be attributed to its modularity 、 Extensibility 、 stability 、 The design tenet of efficiency and performance .RISC-V It's a kind of “ Whiteboard ” Design , There are no restrictions or constraints on traditional or reverse compatibility , Therefore, it can pave the way for the freedom and innovation of open computing design in the future . Thanks to the participation of multiple participants ,RISC-V It is promoting a number of innovations with the help of a variety of open source architecture implementation schemes currently available .

Commercial enterprises require instruction set architecture to remain stable even for products that have been deployed for many years . To solve this problem ,2015 year RISC-V The foundation (RISC-VFoundation) establish , Responsible for development 、 Maintain and release RISC-V Definition . In order to play a better role , This non-profit organization was founded in 2020 Renamed as RISC-V International.

RISC-V It is experiencing exponential growth . According to the RISC-V International The report 1 ,“ Promise to join RISC-V And for RISC-V Investment continues to soar .2021 year ,RISC-V The number of members has increased 130%, achieve 2,478 Members of the team , These include 18 Senior members ”. With billions of chips deployed , From embedded cars to super large-scale artificial intelligence (AI)、 from 5G To high performance computing (HPC) etc. ,RISC-V It has been widely used in all walks of life and various implementation schemes .

RISC-V The open source nature of open standards opens a new era of processor innovation through open standards cooperation . Many participants are promoting the innovation of the implementation scheme , Make the wide open source ecosystem rise rapidly . The ecosystem covers complex hardware design and verification tools 、 A rich suite of software development tools 、 operating system (OS) And real-time operating system (RTOS) Port, etc . Hard core and soft core RISC-V The proliferation of processors also provides great convenience for the transplantation of applications between different implementation schemes and the long-term maintenance of applications . People will see , From the beginning, it is to make full use of RISC-V There will be a large number of applications developed based on the advantages of architecture .

Just FPGA for , One or more soft core processors may be instantiated in the programmable logic of the device , So that designers can integrate the programmable microcontroller and / Or a microprocessor core added to your design . Again , For the direct integration of a 、 Two or four Arm Intel hard core processors System on chip (SoC) FPGA Come on , If necessary, more soft core processors can be instantiated in the programmable logic of the device .

since 2004 Since its launch in , Intel 32 position Nios II The processor has always been Intel FPGA and SoC FPGA The soft core processor chosen by the designers of . these years ,Nios II Processor accumulation formed by developers 、 Tools 、 Software and software IP A large ecosystem of modules .

Now? , Intel has launched open source based RISC-V Instruction set architecture 、 For Intel FPGA A new generation of soft core processors Nios V processor .Nios V The first product of the processor family was Nios V/m(“ Micro controller ” edition ). Intel plans to add more Nios V Processor variants , Including a “ Universal ” edition 、 One “ Application class ” Version and a “Linux” edition , among “Linux” Version is able to run Linux Kernel 64 Bit processor . Besides , Intel will also increase its support for Zephyr、FreeRTOS and Linux Including a wide range of operating system support .

utilize Nios In the processor RISC-V Will greatly expand the current wide range of Nios The ecological system , Based on FPGA More flexibility for system developers 、 Better performance .Nios V The processor uses and Nios II The same simple design process as the processor , Available through Intel Quartus Prime Pro Edition Software get . Make existing based on Nios II The creators of processor design are particularly interested in , They can design quickly 、 Easily migrate to Nios V processor . because RISC-V Several architecture upgrades have been implemented within the instruction set architecture , Compared with the existing soft core processors ,Nios V Soft core processors can provide better performance . Besides ,RISC-V There is another key advantage , That is software portability and stability . for instance , Developers can take advantage of the soft core version RISC-V stay FPGA Start a design in , Anything written at the beginning RISC-V The software running on the soft core can be used in any other RISC-V Run on the core .

RISC-V Another very important advantage is , A broad open source ecosystem is rapidly emerging . This ecosystem includes hardware design and verification tools 、 Software development tools ( Such as compilers and debuggers )、 operating system (OS) and RTOS Port, etc .

Intel invests heavily RISC-V An example of this is , Intel through and well-known RISC-V Tool suppliers and RISC-V International member Ashling cooperation , towards FPGA Customers provide services for RiscFree A complete open source tool solution for integrated development environment and unified debugger .

RiscFree about FPGA

and ASIC Customer value

Today, SoC And system level packaging (SiP) Design is becoming more and more complex , This is because chip designers need to integrate more functions into a single device and a single package , To meet the market for more features 、 The need for higher performance and lower power consumption . There is a bottleneck due to the improvement of the manufacturing process , Designers have to constantly adopt multi-core design . Besides , They also have a variety of heterogeneous processor architectures ( Such as RISC-V、Arm and x86) Integrate into the same SoC or SiP in .

prompt RISC-V A major factor in success is , Different companies and entities can use the instruction set architecture as their own unique differentiated implementation solutions ( For example, different data widths 、 Pipe width and pipe structure ) The basis of . This makes RISC-V Processors can come in a wide variety of forms , From the edge oriented microcontroller application based on 32 position FPGA To cloud based high performance computing applications 64 position SoC Hard core processor for , Everything is contained therein .

Ashling Of RiscFree Integrated development environment and unified debugger are all RISC-V Implementation provides support . Since its launch ,RiscFree The tool chain has steadily won market share in the embedded tool market , stay RISC-V It is easier to use in the market 、 A wide range of functions and plug-in architecture .

RiscFree A single commissioning probe can be used for the above equipment , Provide full open source multi-core from a single software environment ( Isomorphism and isomerism ) Debugging solutions , by ASIC Customers bring added value .RiscFree Fully support Nios V processor , It can also be FPGA Customers bring added value .

Just intel FPGA for ,RiscFree Including an open source 、 be based on Eclipse Integrated development environment 、 compiler 、 Debugger and tracker . This single installation program is available out of the box , Can be based on RISC-V All of the instruction set architecture 32 Bit and 64 position Nios V Soft core processors provide RiscFree Software development and debugging support .

In addition to custom integration and support to Nios V Processor extensions ,RiscFree It also supports Intel Agilex 、 Intel Stratix 10、 Intel Arria 10 Intel Cyclone 10 GX equipment , And more product lines in the future .

Ashling Intel The value of cooperation

since 1982 Since then ,Ashling Has been an important provider of embedded development tools and services , with 30 Years of embedded system tool development experience . As RISC-VInternational Long term members of ,Ashling Always pay close attention to RISC-V The development of , Pay special attention to commissioning standards and tracking standards . As the tracking Technical Committee (Tracecommittee) Vice chairman of ,Ashling Participated in the formulation of the first batch of definitions RISC-V Standards for real-time tracking .

And Ashling cooperation , Intel has its own tool provider , To ensure that all Nios V The tool requirements of the processor can be met , Including the integrated development environment 、 compiler 、 Debugger and Nios V The processor and Arm A complete open source tool chain composed of processor tracking support .

The two companies have planned to maintain long-term cooperation , therefore , With Intel Nios V The development of processor family , The tool chain will also develop , To ensure full support for new products and features .

Ashling Working with the Intel team on engineering will ensure Ashling Software development and Intel FPGA The development tool chain is tightly coupled , for example :

01

Project manager and build manager include Make and Cmake Support , Can quickly import 、 Build and debug Intel Quartus Application framework created by software .

02

Nios V GCC The compiler toolchain is fully integrated into RiscFree In an integrated development environment , Can be used for Nios V HAL API Access to hardware newlib and picolibc Runtime libraries support .

03

RiscFree Provide runtime debugging function , Can support Intel FPGA Download Cable II (USB Blaster II)、Nios V and Arm Processor kernel register virtualization , And right Nios V and Arm Real time on-chip and off chip tracing of two processor cores .

04

RiscFree Also for Zephyr、FreeRTOS、uC/OS-II And a complete goal ( Multicore / many Hart)Linux Kernel, etc OS and RTOS The solution provides perceptual debugging capabilities , It also supports device driver and application debugging .

05

RiscFree Support for Nios V Custom instructions and extensions for processors .

In many cases Arm and RISC-V Processor kernel ( Hard core and / Or soft core ) In the development environment , You must use multiple debuggers , One for Arm processor , One for RISC-V processor . By comparison , Single RiscFree The instance supports debugging any number of heterogeneous or homogeneous kernels ; for example , Also debug Intel FPGA Arm Hard core and Nios V Soft nucleus .

Intel and competitors

Most competitors offer only closed source proprietary solutions , Intel will give you full access to open source RISC-V Ecosystem support . The solution currently supports RISC-V Development , The subsequent deployment to Intel is also supported FPGA、 Intel's structured ASIC And Intel wafer foundry services ASIC.

stay Ashling And its RiscFree Under the support of integrated development environment and unified debugger , Intel as an open ecosystem partner , You can use it RISC-V Easy to use open source tools currently available to developers , Support complete spanning FPGA、 Intel eASIC Equipment and ASIC Custom logical continuum for .

summary

Besides supplying powerful microprocessors to the world , Intel has also developed advanced FPGA.FPGA It can be configured to perform a variety of functions , Including instantiating one or more soft core processors . The performance of these soft core processors is becoming more and more important in the embedded market .

RISC-V Is an open source hardware instruction set architecture .RISC-V Defined as a kind of “ Whiteboard ” Design , There are no restrictions or constraints on traditional or reverse compatibility , Its design aim is to realize modularization 、 Extensibility 、 stability 、 Efficiency and performance . therefore ,RISC-V It is experiencing exponential growth .

Intel joins the global open hardware standards organization RISC-V International, Actively play a leading role , Committed to expanding... For all industry stakeholders RISC-V The potential of ecosystems .

Intel has now released open source based RISC-V Instruction set architecture 、 For Intel FPGA A new generation of soft core processors Nios V processor . In addition to facing FPGA The soft core of Nios V processor , Intel will also provide for Intel eASIC Equipment and ASIC The hard core of RISC-V Implementation scheme . Besides , Intel also offers services from FPGA To Intel eASIC Equipment and ASIC Migration path for . Besides intel , It is difficult for other companies to provide services from FPGA To Intel eASIC The equipment goes to ASIC These can reduce costs 、 Reduce power consumption 、 Migration path to improve performance .

Intel's partner Ashling yes RISC-V International Long term members of ,Ashling Of RiscFree Integrated development environment and unified debugger are all RISC-V Implementation provides support . Since its launch ,RiscFree Tool chains rely on their ease of use 、 Extensive functionality and plug-in architecture , Include RISC-V The embedded tool market, including the market, is widely used .

Ashling Of RiscFree Be able to use a single commissioning probe for the above equipment , Provide full open source multi-core from a single software environment ( Isomorphism and isomerism ) Debugging solutions , For Intel FPGA and ASIC Customers bring added value .

Intel plans to invest more , To strengthen RISC-V Ecosystem construction and promotion RISC-V Further landing . Under the organization of Intel , These investments will help groundbreaking RISC-V The company optimizes through technical collaboration 、 Preferred wafer sharing service 、 Support customer design 、 Cooperate in the establishment of development boards and the development of software infrastructure , Faster innovation .

Scan the QR code immediately or click the link to read the original text , Download the full version for free 《 Intel joins hands with the world famous RISC-V Tool provider Ashling, Focus on expanding multi platform RISC-V Support 》 white paper !

边栏推荐

- Interrupt and polling

- 边缘和物联网学术资源

- sed -i命令怎么使用

- TUIKit 音视频低代码解决方案导航页

- 32-way telephone +2-way Gigabit Ethernet 32-way PCM telephone optical transceiver supports FXO port FXS voice telephone to optical fiber

- How deci and Intel can achieve up to 16.8x throughput improvement and +1.74% accuracy improvement on mlperf

- Quarkus+saas multi tenant dynamic data source switching is simple and perfect

- 中断和轮询

- leetcode:242. 有效的字母异位词

- Digraph D and e

猜你喜欢

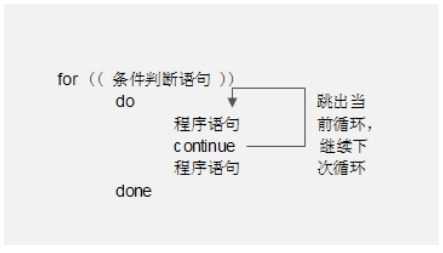

『忘了再学』Shell流程控制 — 39、特殊流程控制语句

Quickly understand the commonly used asymmetric encryption algorithm, and no longer have to worry about the interviewer's thorough inquiry

What is the principle of live CDN in the process of building the source code of live streaming apps with goods?

One way linked list implementation -- counting

Hanyuan hi tech 8-way telephone +1-way 100M Ethernet RJ11 telephone optical transceiver 8-way PCM telephone optical transceiver

#云原生征文#深入了解Ingress

16 channel HD-SDI optical transceiver multi channel HD-SDI HD video optical transceiver 16 channel 3g-sdi HD audio video optical transceiver

【课程预告】基于飞桨和OpenVINO 的AI表计产业解决方案 | 工业读表与字符检测

Digraph D and e

Quartus II 13.1 detailed installation steps

随机推荐

MIT 6.031 Reading5 : Version Control学习心得

How deci and Intel can achieve up to 16.8x throughput improvement and +1.74% accuracy improvement on mlperf

Filtre de texte en ligne inférieur à l'outil de longueur spécifiée

How to solve the task cache compilation problem caused by gradle build cache

PHP handwriting a perfect daemon

何小鹏:如果可以回到创业的时候 不会以自己的名字给产品命名

Cloud native essay deep understanding of ingress

构建英特尔 DevCloud

leetcode:42. Rain water connection

Stick to five things to get you out of your confusion!

Online text filter less than specified length tool

Understand ADT and OOP

逆向调试入门-了解PE结构文件

Use openvinotm preprocessing API to further improve the reasoning performance of yolov5

MySQL single database and table splitting using MYCAT

16 channel HD-SDI optical transceiver multi channel HD-SDI HD video optical transceiver 16 channel 3g-sdi HD audio video optical transceiver

边缘和物联网学术资源

从类、API、框架三个层面学习如何设计可复用软件的学习心得

leetcode:42.接雨水

人脸注册,解锁,响应,一网打尽