当前位置:网站首页>门级建模—学习笔记

门级建模—学习笔记

2022-06-28 03:08:00 【江南小作坊】

门的类型

- 逻辑电路可以使用逻辑门来设计。Verilog语言预定义了一些逻辑门,来支持用户使用。

- 基本的逻辑门分两类:

- 与/或门类(and/or)

- 缓冲器/非门类(buf/not)

与门和或门

与门、或门都具有一个标量输出端和多个标量输入端。

同属与/或门类的门术语有:

- and 与门

- or 或门

- xor 异或门

- nand 与非门

- nor 或非门

- xnor 同或门

逻辑符号如下

其真值表

Verilog实例引用

// 定义端口 wire OUT,IN1,IN2; // 基本门的实例引用 and a1(OUT,IN1,IN2); nand na1(OUT,IN1,IN2); or or1(OUT,IN1,IN2); nor nor1(OUT,IN1,IN2); xor x1(OUT,IN1,IN2); xnor nx1(OUT,IN1,IN2); // 超过两个,三输入端与非门 nand nal_3inp(OUT,IN1,IN2,IN3); //实例引用门,不给实例命名,也是合法的 and (OUT,IN1,IN2);

缓冲器/非门

buf/not门具有一个标量输入和多个标量输出(与and/or门相反)。我们只讨论一个输入和一个输出的buf/not门,对于具有多个输出端的,所有输出端的值都是相同的。

两个基本门的术语

- buf

- not

逻辑符号

真值表

注意:buf和not可以具有多个输出端口,但只能有一个输入端口,输入端口必须是端口列表中的最后一个。

实例引用

buf b1(OUT1,IN); not n1(OUT1,IN); // 两个输出端口 buf b1_2out(OUT1,OUT2,IN); // 实例不命名的引用,合法 not (OUT1,IN);带控制端的缓冲器和非门(bufif/notif)

4个带有控制信号端口的buf/not门

- bufif1

- bufif0

- notif1

- notif0

只有在控制信号有效的情况下才能传送数据,如果控制端无效,则输出为高阻抗z。

逻辑符号

真值表

实例引用

bufif1 b1(out, in ,ctrl); bufif0 b0(out, in ,ctrl); notif1 n1(out, in ,ctrl); notif0 n0(out, in ,ctrl);

在某些情况下,例如当一个信号由多个驱动器驱动时,我们设计驱动源的时候,把控制信号的有效时间相互错开,避免一条信号线同时被两个源驱动。这时就需要带有控制端的缓冲器/非门来搭电路。

设计实例

门级多路选择器

- 设计一个有两位选择信号的四选一多路选择器,假设选通信号s1和s0不能为x或z值,其结构图和真值表如下

- 可以使用几种基本类型的逻辑门来实现多路选择器

- Verilog实现

- RTL视图

- 编写仿真激励模块

- 仿真结果

- 设计一个有两位选择信号的四选一多路选择器,假设选通信号s1和s0不能为x或z值,其结构图和真值表如下

四位脉动进位全加器

实现一个脉动进位加法器,它的基本组成部分是一个全加器,全加器的数学表示如下: s u m = ( a ⊗ b ⊗ c i n ) sum=(a\otimes b \otimes cin ) sum=(a⊗b⊗cin) c o u t = ( a ⋅ b ) + c i n ⋅ ( a ⊗ b ) cout=(a\cdot b)+ cin \cdot (a \otimes b ) cout=(a⋅b)+cin⋅(a⊗b)

一位全加器的逻辑图

一位全加器的Verilog描述

四位脉动进位全加器可以用四个一位全加器构成,如下图

Verilog实现

仿真激励

`timescale 1ns/1ps module fulladd4_tb(); reg [3:0] A,B; reg C_IN; wire [3:0] SUM; wire C_OUT; fulladd4 FAL_4(SUM, C_OUT, A, B, C_IN); // 设置信号监视 initial begin $monitor($time,"A=%b,B=%b,C_IN=%b, --- C_OUT=%b,SUM=%b\n", A,B,C_IN,C_OUT,SUM); end // 输入激励信号 initial begin A=4'd0; B=4'd0; C_IN=1'b0; #5 A=4'd3; B=4'd4; #5 A=4'd2; B=4'd5; #5 A=4'd9; B=4'd9; #5 A=4'd10; B=4'd15; #5 A=4'd10; B=4'd5; C_IN=1'b1; end endmodule仿真结果

门延迟

- 上面描述的电路都是无延迟的(零延迟)。但是,在实际电路中,任何一个逻辑门都是有延迟的。Verilog可以用过门延迟来说明逻辑电路中的延迟。

三种延迟

- 上升延迟:在门的输入发生变化的情况下,门的输出从0,x,z变化为1所需的时间。

- 下降延迟:门的输出从1,x,z变化为0所需的时间。

- 关断延迟:指门的输出从0,1,x变化为高阻抗z所需的时间。

- 注意:

- 如果值变化到不确定值x,则所学的时间可以看成是以上三种延迟值最小的那个。

- 三种不同的方法说明门的延迟

- 只指定一个,则所有类型的延迟都是用这个值;

- 指定两个(上升与下降),则关断延迟为两者的最小者;

- 指定三个,即每个延迟都说明。

最小/典型/最大延迟

- 除了可以指定上面所述的三种类型的延迟外,对每种类型的延迟还可以指定其最小、最大值和典型值。用户可以在仿真一开始时就决定具体选择使用哪一种延迟。

- 举例说明

设计实例

边栏推荐

猜你喜欢

随机推荐

第九章 APP项目测试(3) 测试工具

基于 WPF 的酷炫 GUI 窗口的简易实现

Set drop-down options on Excel files

多线程与高并发二:volatile和CAS详细介绍

力扣每日一题-第29天-1491.去掉最低工资和最高工资后的平均工资

【PaddleDetection】ModuleNotFoundError: No module named ‘paddle‘

Custom controls under WPF and adaption of controls in Grid

Execution plan in MySQL of database Series

小程序image组件不显示图片?

"Five layer" architecture of cloud applications and services

基于 LNMP 搭建个人网站的填坑之旅

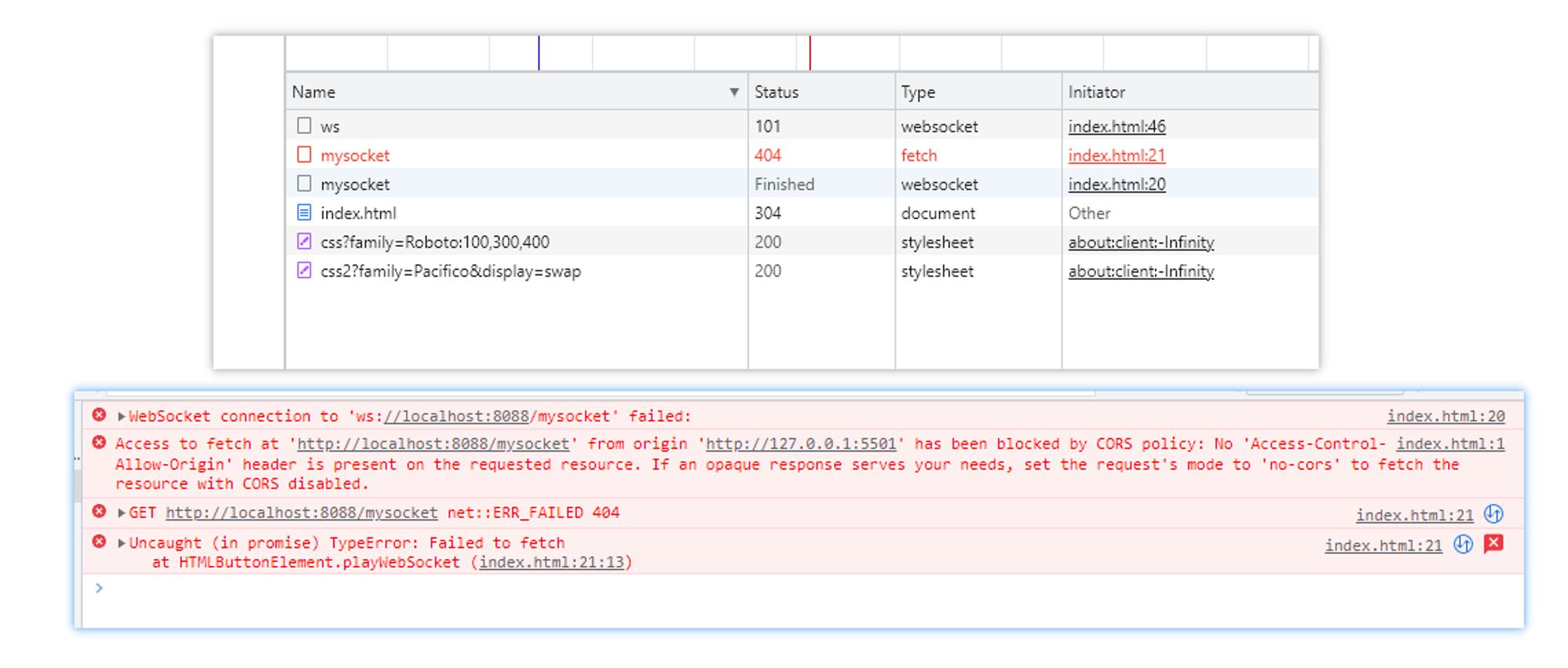

Websocket (simple experience version)

The same is MB. Why is the gap so large?

密码加密md5和加盐处理

数据库系列之MySQL和TiDB中慢日志分析

从遇见大咖到成为大咖,昇腾AI开发者创享日给开发者带来无限可能

Is Guotai Junan Securities reliable? Is it safe to open a securities account?

applicationContext.getBeansOfType 获取一个接口下所有实现类 执行方法或者获取实现类对象等 操作应用场景学习总结

How does the open-ended Hall current sensor help the transformation of DC power distribution?

WARN:  SQL  Error: …