当前位置:网站首页>第六章 习题(678)【微机原理】【习题】

第六章 习题(678)【微机原理】【习题】

2022-06-25 22:02:00 【日星月云】

前言

以下内容源自微型计算机原理(第四版)王忠民主编

仅供学习交流使用

请您阅读文章声明,默认同意该声明

推荐

第六章 习题

负逻辑与门

符号

就是正逻辑与门的输入输出端加小圆圈

真值表

先说正逻辑与门

正逻辑与门真值表

0无效1有效

只有全1才为1

| A | B | C |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

负逻辑与门真值表

0有效1无效

只有全0才为0

| A | B | C |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

其和正逻辑的或门真值表相同

6

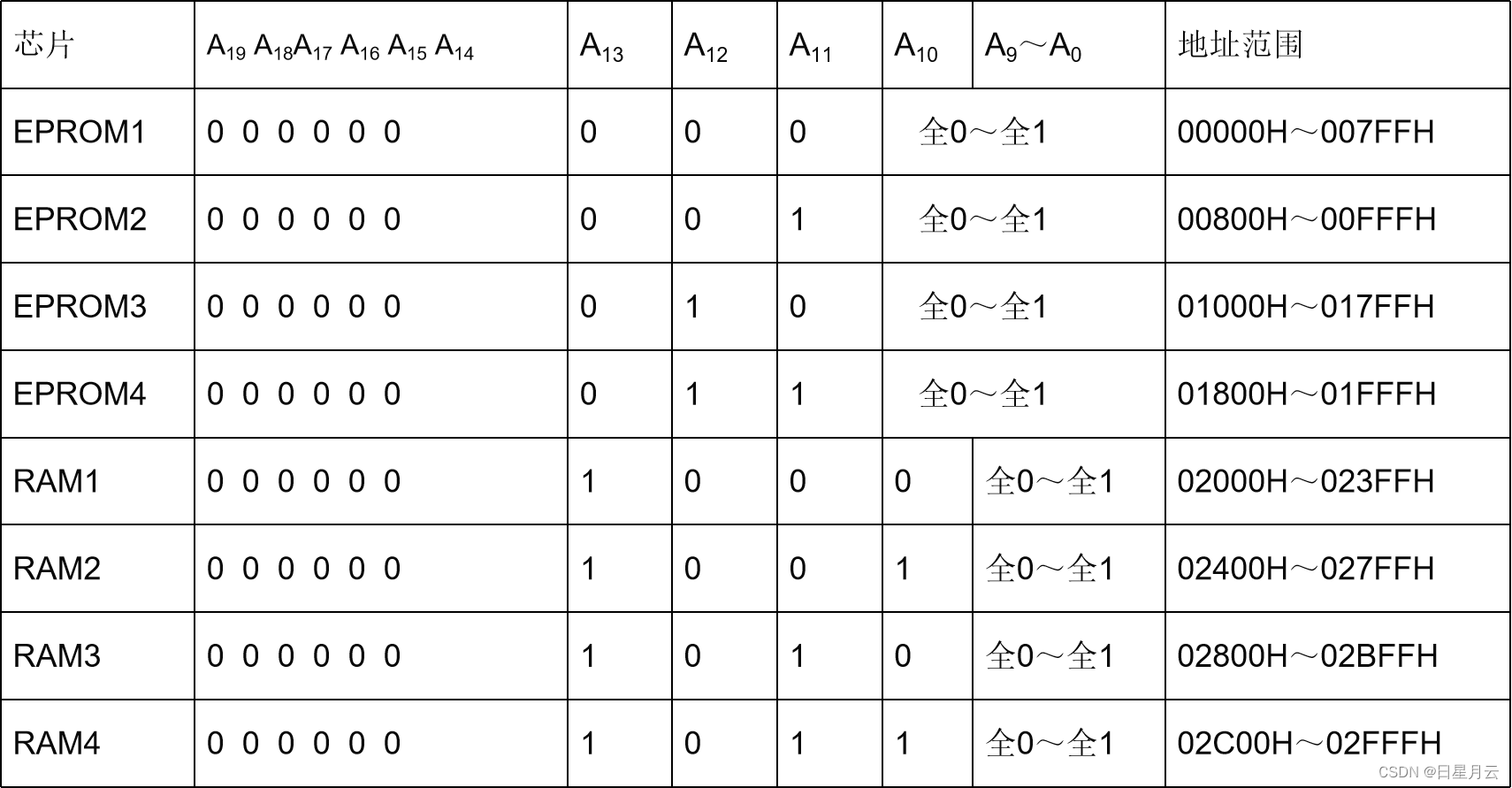

6、已知:8位微机地址,总线16位,设计12KB存储系统,其中ROM 占用0000H开始的8KB,RAM占用2000H 开始的4KB,存储芯片分别选用INTEL 2716和2114

分析如下:

(1)

ROM 8Kx8 2716 2K×8芯片,需4片,做字扩展,片内寻址线11根

RAM 4kx8 2114 1K×4芯片,需8片,做字位扩展,片内寻址线10根

(2)地址范围: A15 A14 A13 A12 A11 A10 A9~A0

0k

ROM1:0000H~07FFH 0 0 0 0 0 全0~全1

+2K

ROM2:0800H~0FFFH 0 0 0 0 1 全0~全1

+2K

ROM3:1000H~17FFH 0 0 0 1 0 全0~全1

+2K

ROM4:1800H~1FFFH 0 0 0 1 1 全0~全1

8k

RAM1、2:2000H~23FFH 0 0 1 0 0 0 全0~全1

+1K

RAM3、4:2400H~27FFH 0 0 1 0 0 1 全0~全1

+1K

RAM5、6:2800H~2BFFH 0 0 1 0 1 0 全0~全1

+1K

RAM7、8:2C00H~2FFFH 0 0 1 0 1 1 全0~全1

12k

(3)

A13 A12 A11 3:8译码器 译码输入 (一级译码)

0 0 0 ROM1 :!Y0

0 0 1 ROM2 :!Y1

0 1 0 ROM3 :!Y2

0 1 1 ROM4 :!Y3

1 0 0 RAM1、2 :!Y4 与 A10 (二级译码) 此与是负逻辑与

0

1 0 0 RAM3、4 :!Y4 与 A10

1

1 0 1 RAM5、6 :!Y5 与 A10

0

1 0 1 RAM7、8 :!Y5 与 A10

1

忽略以下

(3)

A13 A12 A11 A10 4-16译码器 译码输入 (一级译码)

0 0 0 1 ROM1 :!Y1

0 0 1 1 ROM2 :!Y3

0 1 0 1 ROM3 :!Y5

0 1 1 1 ROM4 :!Y7

1 0 0 0 RAM1、2 :!Y8

1 0 0 1 RAM3、4 :!Y9

1 0 1 0 RAM5、6 :!Y10

1 0 1 1 RAM7、8 :!Y11

忽略以上

(4)画图连接

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2716

2716

2716

2716

7

7现有Inter 6264(8 K X 8)静态RAM存储器芯片若干,要求设计一个64K X 8的存储器系统,其地址总线为16位(A0 ~ A15),地址范围为0000~FFFFH。

分析如下:

(1)

RAM 64K X 8 6264 8 K X 8芯片 需要8片,做字扩展,片内寻址线13根

(2)地址范围: A15 A14 A13 A12~A0

0k

RAM1 0000H~1FFFH 0 0 0 全0~全1

+8k

RAM2 2000H~3FFFH 0 0 1 全0~全1

+8k

RAM3 4000H~5FFFH 0 1 0 全0~全1

+8k

RAM4 6000H~7FFFH 0 1 1 全0~全1

+8k

RAM5 8000H~9FFFH 1 0 0 全0~全1

+8k

RAM6 A000H~BFFFH 1 0 1 全0~全1

+8k

RAM7 C000H~DFFFH 1 1 0 全0~全1

+8k

RAM8 E000H~FFFFH 1 1 1 全0~全1

64k

(3)

A15 A14 A13 3:8译码器 译码输入 (一级译码)

0 0 0 RAM1 :!Y0

0 0 1 RAM2 :!Y1

0 1 0 RAM3 :!Y2

0 1 1 RAM4 :!Y3

1 0 0 RAM5 :!Y4

1 0 1 RAM6 :!Y5

1 1 0 RAM7 :!Y6

1 1 1 RAM8 :!Y7

(4)画图连接

字扩展 A15 A14 A13 3-8译码器 CS

6264

6264

6264

6264

6264

6264

6264

6264

8

8.某一微机系统的CPU字长为8位,地址信号线为16根。上电复位后,程序计数器

PC指向0000H地址的存储单元。要求使用2716 EPROM芯片(2Kx8)组成4KB的ROM存放系统监控程序,并预留4KB的用户ROM空间;使用2114SRAM芯片(1Kx4)组成8KB系统及用户RAM。试设计该机的存储器系统。

(1)

ROM 8K X 8 2716 2 K X 8芯片 需要4片,做字扩展,片内寻址线11根

RAM 8K X 8 2114 1 K X 4芯片 需要16片,做字位扩展,片内寻址线10根

(2)地址范围: A15 A14 A13 A12 A11 A10 A9~A0

0k

ROM1:0000H~07FFH 0 0 0 0 0 全0~全1

+2K

ROM2:0800H~0FFFH 0 0 0 0 1 全0~全1

+2K

ROM3:1000H~17FFH 0 0 0 1 0 全0~全1

+2K

ROM4:1800H~1FFFH 0 0 0 1 1 全0~全1

8k

RAM1、2:2000H~23FFH 0 0 1 0 0 0 全0~全1

+1K

RAM3、4:2400H~27FFH 0 0 1 0 0 1 全0~全1

+1K

RAM5、6:2800H~2BFFH 0 0 1 0 1 0 全0~全1

+1K

RAM7、8:2C00H~2FFFH 0 0 1 0 1 1 全0~全1

+1K

RAM9、10:3000H~33FFH 0 0 1 1 0 0 全0~全1

+1K

RAM11、12:3400H~37FFH 0 0 1 1 0 1 全0~全1

+1K

RAM13、14:3800H~3BFFH 0 0 1 1 1 0 全0~全1

+1K

RAM15、16:3C00H~3FFFH 0 0 1 1 1 1 全0~全1

16K

(3)

A13 A12 A11 3-8译码器 译码输入 (一级译码)

0 0 0 ROM1 :!Y0

0 0 1 ROM2 :!Y1

0 1 0 ROM3 :!Y2

0 1 1 ROM4 :!Y3

1 0 0 RAM1、2 :!Y4 与 A10 (二级译码) 此与是负逻辑与

0

1 0 0 RAM3、4 :!Y4 与 A10

1

1 0 1 RAM5、6 :!Y5 与 A10

0

1 0 1 RAM7、8 :!Y5 与 A10

1

1 1 0 RAM9、10 :!Y6 与 A10

0

1 1 0 RAM11、12 :!Y6 与 A10

1

1 1 1 RAM13、14 :!Y7 与 A10

0

1 1 1 RAM15、16 :!Y7 与 A10

1

忽略以下

(3)

A13 A12 A11 A10 4-16译码器 译码输入 (一级译码)

0 0 0 1 ROM1 :!Y1

0 0 1 1 ROM2 :!Y3

0 1 0 1 ROM3 :!Y5

0 1 1 1 ROM4 :!Y7

1 0 0 0 RAM1、2 :!Y8

1 0 0 1 RAM3、4 :!Y9

1 0 1 0 RAM5、6 :!Y10

1 0 1 1 RAM7、8 :!Y11

1 1 0 0 RAM9、10 :!Y12

1 1 0 1 RAM11、12 :!Y13

1 1 1 0 RAM13、14 :!Y14

1 1 1 1 RAM15、16 :!Y15

忽略以上

----16k

字扩展 A13 A12 A11 A10 3-16译码器 控制cs

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

2114 | 2114

----8k

2716

2716

----4k

2716

2716

最后

请您阅读文章声明,默认同意该声明

打赏通道

边栏推荐

- UE4 学习记录二 给角色添加骨架,皮肤,及运动动画

- Multithreaded learning 2- call control

- hiberate核心API/配置文件/一级缓存详解

- [opencv450 samples] read the image path list and maintain the proportional display

- hiberate架构介绍及环境搭建(非常详细)

- Idea shortcut

- 字符串

- LeetCode-1528-重新排列字符串-哈希表-字符串

- Pointer strengthening and improvement

- Konva series tutorial 2: drawing graphics

猜你喜欢

![[opencv450 samples] inpaint restores the selected region in the image using the region neighborhood](/img/36/8ad6034473382f66f315eb70440711.png)

[opencv450 samples] inpaint restores the selected region in the image using the region neighborhood

hiberate实体类CURD、事务操作汇总

提取系统apk

CSDN add on page Jump and off page specified paragraph jump

Idea shortcut

Hibernate entity class curd, transaction operation summary

Qt 中文和英文分别使用不同的字体

Visual studio code create minimal web API (asp.net core)

Hbuilderx uses the gaude map to obtain the current location

UE4_ Ue5 combines the offline voice recognition plug-in for speech recognition

随机推荐

What is Unified Extensible Firmware Interface (UEFI)?

Repoptimizer: it's actually repvgg2

解决‘tuple‘ object has no attribute ‘lower‘

CSDN add on page Jump and off page specified paragraph jump

CTS RTS RX TX in serial port flow control UART (direct communication between serial port module and MCU)

RK3568+鸿蒙工控板工业网关视频网关解决方案

Leetcode (605) -- flower planting

C2. k-LCM (hard version)-Codeforces Round #708 (Div. 2)

Ble Low Power Bluetooth networking process and Bluetooth role introduction

Customize the qcombobox drop-down box, right align the display, and slide the drop-down list

Windows redis installation and simple use

Idea FAQ collection

做接口测试,这3种工具到底什么时候用?

What is Unified Extensible Firmware Interface (UEFI)?

二进制、16进制、大端小端

(serial port Lora module) centrida rf-al42uh private protocol test at instruction test communication process

UE4 学习记录二 给角色添加骨架,皮肤,及运动动画

B. Box Fitting-CodeCraft-21 and Codeforces Round #711 (Div. 2)

QLabel 文字水平滚动显示

记一次beego通过go get命令后找不到bee.exe的坑