当前位置:网站首页>FPGA project development: experience sharing of lmk04821 chip project development based on jesd204b (I)

FPGA project development: experience sharing of lmk04821 chip project development based on jesd204b (I)

2022-06-24 16:36:00 【FPGA technology Jianghu】

FPGA Project development : be based on JESD204B Of LMK04821 Chip project development experience sharing ( One )

Hello, great Xia , o Q Come on , I'll meet you for the first time today , Please take care of me . Today, I'd like to share my project development experience with you “ be based on JESD204B Of LMK04821 Chip project development ( One )”, This is my real project development experience , I hope it can provide some reference and learning function for the great Xia in need .

There are many opportunities in the future , Slowly share some project development and learning content , Welcome to exchange views with you . I have settled in “FPGA Technical Jianghu ” special column , If you have any questions about this article and the subsequent updates, please communicate with me , Welcome to “FPGA Technical Jianghu ” In the column . Don't talk much , Loading .

One 、 LMK04821 Function is introduced

LMK0482X Series is a high performance clock regulation chip series launched by Texas Instruments , There are currently three types of this chip , Respectively LMK04821、LMK04826 as well as LMK04828, All chips in this series support the latest JESD204B agreement . This debugging mainly focuses on LMK04821 For example , Summarize and explain some problems in the debugging process .

Its performance is described as follows :

Support JESD204B;

Ultra low clock jitter and noise ;

It can output at the same time 14 Three differential clocks :

<1>. 7 Yes, we can JESD204B Of SYSREF The clock ;

<2>. The maximum output frequency can reach 3.1GHz;

<3>. The level standard of output differential clock is programmable :LVPECL、LVDS、HSDS、 as well as LCPECL;

double PLL structure ;

PLL2 Of VCO The frequency division coefficient is 1-32;

Output clock precise digital delay 、 Analog delay 、 And dynamic delay ;

Multiple working modes : double PLL、 single PLL And clock distribution mode ;

LMK0482X The difference between these three chips is that they support different VCO, As shown in the figure below 1 Shown :

LMK04821 The application diagram of the chip is shown in the figure below 2 Shown :

LMK0482X The pin distribution definition of is shown in the figure below 3 Shown , It's important to know the function of each pin , One by one :

PIN1、2: The first 0 road Device CLK Differential output ;

PIN3、4: The first 1 road SYSREF/Device CLK Differential output ;

PIN5: The reset input of the chip is universal GPIO;

PIN6: The clock synchronization input port of the chip is either continuous SYSREF CLK Request input port ;

PIN7、8、9: useless , Just hang in the air ;

PIN10: Power input ;

PIN11:LDO Bypass capacitance , external 10uf To the ground ;

PIN12:LDO Bypass capacitance , external 0.1uf To the ground ;

PIN13、14: The first 3 road SYSREF/Device CLK Differential output ;

PIN15、16: The first 2 road Device CLK Differential output ;

PIN17: Power input ;

PIN18: Chip SPI To configure CS The signal ;

PIN19: Chip SPI To configure SCK The signal ;

PIN20: Chip SPI To configure SDIO The signal ;

PIN21: Power input ;

PIN22、23: The first 5 road SYSREF/Device CLK Differential output ;

PIN24、25: The first 4 road Device CLK Differential output ;

PIN26: Power input ;

PIN27、28: The first 6 road Device CLK Differential output ;

PIN29、30: The first 7 road SYSREF/Device CLK Differential output ;

PIN31: Programmable condition monitoring I/O Pin ;

PIN32:PLL1 Charge pump output of ;

PIN33: Power input ;

PIN34、35:PLL1 The reference clock input of 1、 External feedback clock input in zero delay mode 、 external VCO Input ;

PIN36: Power input ;

PIN37、38:PLL1 The reference clock input of 0;

PIN39: Power input ;

PIN40、41: Feedback to PLL1, Reference input to PLL2.AC coupling ;

PIN42: Power input ;

PIN43、44:PLL2 The reference clock input of 、PLL1 Feedback clock input ;

PIN45: Power input ;

PIN46:PLL2 Charge pump output of ;

PIN47: Power input ;

PIN48: Programmable condition monitoring I/O Pin ;

PIN49、50: The first 9 road SYSREF/Device CLK Differential output ;

PIN51、52: The first 8 road Device CLK Differential output ;

PIN53: Power input ;

PIN54、55: The first 10 road Device CLK Differential output ;

PIN56、57: The first 11 road SYSREF/Device CLK Differential output ;

PIN58: Programmable condition monitoring I/O Pin ;

PIN59: Programmable condition monitoring I/O Pin ;

PIN60、61: The first 13 road SYSREF/Device CLK Differential output ;

PIN62、63: The first 12 road Device CLK Differential output ;

PIN64: Power input ;

DAP : Heat sink , Grounding ;

Two 、 LMK04821 Use steps

2.1 Hardware circuit check

2.1.1 Whether the power supply of the chip is normal , Whether it meets the working conditions of the device , This step directly determines whether the chip can work normally , Refer to the figure below for test points ;

2.1.2 Whether the reference clock input of the chip is normal , Check with the help of an oscilloscope ,CLKin0 The clock of the terminal is provided by an external signal source ,OSCin The clock is provided by the crystal oscillator on the board , Measurement goes into AD Before the clock is normal ;

2.2 Register configuration

LMK04821 Configuration of SPI The way , Its configuration rules extract key knowledge points by reading the data manual , as follows :

2.2.1 When writing operations ,CS When the signal is low ,SDIO Data in SCK The rising edge is written into the chip , Write data in the format of 1bit Read and write control bits of +2bit Of 0+13bit Address +8bit data .

2.2.2 When reading operations , Write... First 1bit Read and write control bits of +2bit Of 0+13bit Address , And then in the next SCK The rising edge of 8bit data ;

The sequence diagram is shown below 6 Shown :

2.2.3 Conduct SPI When writing time series , Be sure to follow the sequence requirements in Figure 7 , besides , stay FPGA Interior design SPI Code must be readable and writable , In this way FPGA When you configure registers, you can know whether the values configured in each register are correct , This step is to control the operation of the whole chip ,FPGA The first step to complete .

2.2.4 LMK04821 The double PLL Introduction of cascade system :

This series of chips are very flexible , commonly JESD204B The system's dual PLL Cascade applications are the most classic , But for traditional applications , The same applies . It should be noted that Device CLK No single ended output , Only OSCout Pins can provide LVCMOS Single ended output . in addition , Except for double PLL Application mode , You can also configure a single PLL Or clock distribution mode .

LMK0482X A series of dual chips PLL The structure ensures that the clock with the lowest jitter can be output in a wide output frequency range . first stage PLL(PLL1) Driven by an external reference clock , Level second PLL(PLL2) from VCXO Or adjustable crystal oscillator to provide high precision 、 Low noise secondary reference clock . After these two levels PLL, The accuracy of the output clock will be greatly improved .

LMK0482X Series of chips output 7 Yes JESD204B DeviceCLK and 7 Yes SYSREF CLK, Each of them Device CLK Corresponding to one SYSREF CLK. For those who are not JESD204B Application ,SYSREF CLK It can also be programmed to Device CLK. PLL1 The input reference clock includes pins CLKin0,CLKin1 as well as CLKin2, Choose any one as the clock input , The selection rules are determined by the configuration register parameters . VCXO/Crystal Cache output ,LMK0482X Series chips provide OSCout Output , The output is actually PLL1 Feedback input for , It's also PLL2 The reference clock input of , The function of the chip is to provide a clock to the controller before programming , Controller programming reconfiguration LMK0482X.OSCout The output can be LVDS、LVPECL as well as LVMOS level .

LMK0482X It has the function of frequency keeping , When the external reference clock is lost , The output frequency can also keep the minimum drift , Until the external reference clock is restored .

7 road Device CLK Can be divided separately , The frequency division coefficient is 1~32.

7 road SYSREF CLK Unified frequency division , The frequency division coefficient is 8~8191.

Device CLK It has the function of delay , It includes analog delay and digital delay . Simulation delay is based on 25ps Unit of clock delay module , Using the module itself also brings 500ps Time delay of . The digital delay range is 4~32 VCO Clock cycle , The size of each delay unit is 0.5 VCO cycle . It should be noted that the delay function will not work until synchronization is enabled .

SYSREF CLK It also has analog core and digital delay . The minimum unit of analog delay is 150ps. The number range for the delay 1.5~11VCO, Similarly, the size of each delay unit is 0.5 VCO cycle .

14 The output of the clock is not only programmable in the level standard , Also programmable in the amplitude of the output .

To make the digital delay of the clock work , Pin SYNC You have to give a pulse , All clocks are synchronized on the rising edge of the pulse .

LMK04821 Several status pins are provided for the user to monitor the internal status of the chip or as input ports to respond to the user's needs , The specific functions are described in the register configuration description .

2.2.5 Functional block diagram

2.2.6 Register configuration order

It's going on LMK04821 Register configuration , A recommended order is given in the manual , As shown in the figure below 9 Shown :

In the auxiliary software TICS Pro in , The generated register order is also configured in strict accordance with the manual .

But in practice , According to the register configuration order , The clock output does not have the correct clock output . In practice , Configure the register order in the following order :

1、0X000 Configure twice , Reset first , then 0X000 To configure 00, No operation ;

2、 And then immediately from 0X100~0X145;

3、0X171~0X17D;

4、0X146~0X16E;

5、0X143(90)、0X149(00)、0X143( two B0、90)、0X144(FF)、0X143( two 10、11)、0X139(03)、0X002(00); Fixed values ; Try not to change , Why do you want to configure like this , Refer to the corresponding data manual .

Be careful : in application , So far, this register order is the only one that can generate the clock correctly , You can refer to the register data given by the software , Try not to change the order of the configuration registers . Some registers are not configured in the design , For example, some read-only registers ,IC Information related registers ,reback The related registers are not configured , It doesn't hurt in practice , You don't have to configure it . But in SPI When configuring registers , If you want to check whether the register read and write is successful , You can read these registers , Make sure SPI Normal operation .

2.2.7 Registers correspond to data

Before that , After determining the register configuration order , Using assistive software TICS Pro The software generates the corresponding parameters , according to 6 Write operations are performed in the register order shown in . The generation of important parameters and how to set them in the software are shown in the figure below 10;

We must master the application of software , Make sure that when you generate the desired clock , How to operate the software , The corresponding coefficients are obtained , How to coordinate each point in the software ; How do parameters correspond to each other , It is suggested to compare with the data manual , Can do more with less .

- Mark 1 choice CLKin0 As a reference clock input ; The hardware environment value is in CLKin0 There is a clock input at the end ;

- Mark 2 choice PLL1,MUX It's optional , Different options , The values to be configured for the corresponding registers are different ;

- Mark 3 Select the appropriate DIV The number , Get the clock you need 100M;

- Mark 4 CPout1 Direct connection to external crystal oscillator , The purpose is , When the reference clock is lost , The delay function can make PLL1 The tuning voltage is fixed at VCXO Or tunable crystal oscillator , So that when the external reference clock is lost , The output clock frequency has the smallest offset , Until the external clock recovers .

- Mark 5 OSCin,PLL1 Feedback input for ,PLL2 The reference clock input of , In actual debugging , Find out OSCin If there is no input , There is no clock output at the output , No, CLKin0 Input , The output clock is still normal ;

- Mark 6、7、8、9、10、11、12, These are all related to PLL2 VCO Frequency It matters , It is shown in the manual LMK04821 In the use of VCO1 when ,PLL2 The frequency requirement is 2920~3080MHz Between .

Out of range , The software will report a red error . In fact, these settings are simple OSCin It is an operation of frequency doubling before frequency division ; such as , In practice, we need DCLKout Output 150M、75M The clock , In the case of compounding the required range , Find a suitable common multiple , In the example is 1500M, thus , You can get 150M Of DCLKoutX Output , And get 75M The clock output of ;

besides , The clock output setting is shown in the figure below 11 Shown :

- Mark 1, Common multiple ;

- Mark 2,PLL1 Feedback input for ,PLL2 Reference input for , In practice ,PLL2 The reference input for is OSCin;

- Mark 3, Division coefficient ,1500M Ten minutes 150M;

- Mark 4, choice PD, Means that the channel does not output , In the off state ;

- Mark 5,DCLK output frequency , You can directly fill in the desired value in the corresponding position . Be careful , It's better to use the integer of common multiple after frequency division , Otherwise , The software will automatically generate a value that is closest to the filled value ;

- Mark 6,SCLK Output port ,SCLK You can't separate the frequencies ,7 Each channel can only be unified for frequency division ; The specific settings are shown in the figure below 12 Shown :

Be careful : When setting register parameters , When operating software , Will be marked in the lower left window 2 The corresponding register and value are displayed at , So that we can quickly find out the configuration of this value in the data manual ;

Software configuration , The most important parameters and corresponding registers are as follows :

- Doubler, Corresponding to the relevant register 0X162;

- R Divider, Corresponding register 0X160、0X161;

- N Divider, Corresponding register 0X168;

- VCO, Corresponding register 0X138;

- DCLKoutX_DIV, Corresponding register 0X100、0X108、0X110、0X1180、0X120、0X128、0X130;

- SYSREF DIV, Corresponding register 0X13A、0X13B.

Be careful ; Some parameters need to be used with multiple registers ; Additional registers are generated during software configuration , According to the specific design requirements for software operation configuration , After exporting the parameters , You can change it in the corresponding register .

3、 ... and 、 Using the results

3.1 Clock output result

In the face of LMK04821 After the chip is properly configured , The clock can output the desired clock frequency normally , Measurement by oscilloscope , Can directly observe the clock output ; Change the frequency division coefficient in the program , It can also get the corresponding clock output at the output end .

3.2 Problems to be solved

Considering the problem of clock homology in the system , In the face of CLKin0 Reference input clock 、DCLK、SCLK The initial phase contrast is observed by oscilloscope , It is found that after frequency multiplication and frequency division , The starting phase of the clock is about 1/4 A period deviation , Multiple tests , Every time there's a slight deviation .

among ,DCLK And SCLK If the output frequency is the same , The phase difference is observed by , There's a slight deviation , In consideration of the oscilloscope use process , Probe instability , The tentative phase deviation is 0; When there are better testing methods in the later stage , And then confirm .

o Q This is the end of the project development experience sharing , Everything is difficult at the beginning , Today has opened the first , We will continue to share more project development experience with you when we have time . Great Xia , I'll see you again , I wish you all the best !

End

It will be updated continuously in the future , bring Vivado、 ISE、Quartus II 、candence Installation related design tutorial , Learning resources 、 Project resources 、 Good article recommendation and so on , I hope great Xia will continue to pay attention to .

The world is so big , Keep going , I wish you all the best , I'll see you again !

边栏推荐

- Serial of H3CNE experiment column - VLAN configuration experiment, access and trunk

- What does the router pin mean?

- How do HPE servers make RAID5 arrays? Teach you step by step today!

- Tencent releases the full platform version of reasoning framework TNN, and supports mobile terminal, desktop terminal and server terminal at the same time

- 企业安全攻击面分析工具

- Global and Chinese markets of natural insect repellents 2022-2028: Research Report on technology, participants, trends, market size and share

- How to select an open source license

- Serial of H3CNE experiment column - spanning tree STP configuration experiment

- There are potential safety hazards Land Rover recalls some hybrid vehicles

- Principle analysis of robot hardware in the loop system

猜你喜欢

B. Terry sequence (thinking + greed) codeforces round 665 (Div. 2)

Ui- first lesson

![[go] concurrent programming channel](/img/6a/d62678467bbc6dfb6a50ae42bacc96.jpg)

[go] concurrent programming channel

A survey on model compression for natural language processing (NLP model compression overview)

C. K-th not divisible by n (Mathematics + thinking) codeforces round 640 (Div. 4)

C. Three displays codeforces round 485 (Div. 2)

ZOJ - 4104 sequence in the pocket

Cognition and difference of service number, subscription number, applet and enterprise number (enterprise wechat)

MySQL進階系列:鎖-InnoDB中鎖的情况

B. Ternary Sequence(思维+贪心)Codeforces Round #665 (Div. 2)

随机推荐

The million bonus competition is about to start, and Ti-One will be upgraded to help you win the championship!

What is cloud development? Why cloud development? Talk about our story

Enterprise service growth path (7): what key factors will affect SaaS' sales performance?

MySQL Innodb和Myisam

Development trend of CAE simulation analysis software

CDs view permission check

How to pop up an alarm through the national standard gb28181 protocol video platform easygbs for mobile detection / perimeter intrusion detection video recording

TRTC web end imitation Tencent conference microphone mute detection

对深度可分离卷积、分组卷积、扩张卷积、转置卷积(反卷积)的理解

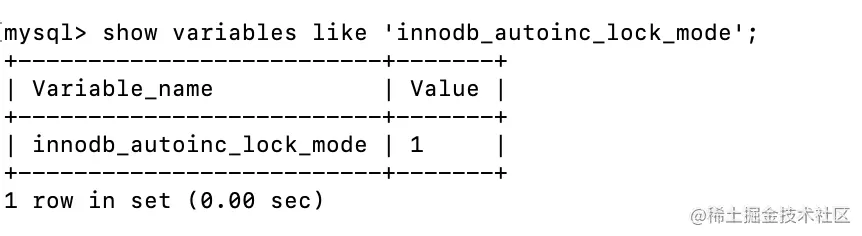

MySQL Advanced Series: Locks - Locks in InnoDB

D. Solve the maze (thinking +bfs) codeforces round 648 (Div. 2)

Istio FAQ: sidecar startup sequence

PyTorch中的转置卷积详解

A survey of training on graphs: taxonomy, methods, and Applications

Serial of H3CNE experiment column - spanning tree STP configuration experiment

AI video structured intelligent security platform easycvr realizes intelligent security monitoring scheme for procuratorate building

Factory mode

Applet - use of template

What is Ethernet

A survey on model compression for natural language processing (NLP model compression overview)