当前位置:网站首页>System Verilog — interface

System Verilog — interface

2022-06-25 14:56:00 【Long water and sky】

Catalog

One 、 Interface

1. Concept

- take interface Think of it as a “ Insert ”,DUT And TB Data driven relationships between can be used interface This arrangement is used to complete .

- interface and module The nature of their use is very similar to . It can define ports , Two way signals can also be defined . He can use initial and always, It can also be defined function and task.

- interface It can be used for design or verification .

2. advantage

- Encapsulate relevant signals in the same interface , It is beneficial to the maintenance and use of the design and verification environment . If you need to add a new signal , Just declare it once in the interface .

- Because of the characteristics that can be instantiated , So that for multiple groups of the same bus , Become more flexible when using and instantiating .

- As SV The only medium of interaction between hardware and software environment in , Both in the hardware world (module) Use in , Or in the software world (class) Use in .

3. Definition and use

Definition :

- Definition and module similar , The instantiation method is the same as module equally .

- stay interface Only the clock needs to be defined in the port list of 、 Reset and other common signals , Or don't define any port signals , Instead, define each need in the variable list DUT and TB Connected logic Variable .

- interface The reusability can be improved by parameterization .

Use :

- Interface signals must be driven using non blocking assignment .

- When using interfaces, be sure to declare interface variables outside of modules and blocks .

- Used in an interface modport Group the signals and specify the direction .

// with modport The interface of

interface arb_if(input bit clk);

logic[1:0]grant, request;

logic rst;

modport TEST(output request, rst,

input grant, clk);

modport DUT(input request, rst, clk,

output grant);

modport MONITOR(input request, grant, rst, clk);

endinterface

// Used in the interface modport Arbiter model

module arb(arb_if.DUT arbif);

...

endmodule

// Used in the interface modport Test platform of

module TEST(arb_if.TEST arbif);

...

endmodule

Two 、 Sampling and driving

1. Competition problem

- In simulation behavior , In order to avoid the timing competition between clock and driving signal in sequential circuit , Drive timing and sampling timing shall be given as clearly as possible .

- By default , The clock will add an infinite minimum time to the driving of the combinational circuit (delta-cycle) Delay of , This delay cannot be measured in absolute time units , Less accurate than the smallest time unit .

- In a time slice (time-slot) Many things can happen in , For example, typing in the simulator “run 0”, That is, let the simulator run a delta-cycle Time for .

How to avoid the competition of sampling ?

- When driving , Add the corresponding artificial delay , Simulate real delay behavior , At the same time, increase clk And the delay between variables , To improve DUT Accuracy and... When using signals TB Reliability when sampling signals .

- For some samples, it still exists delta-cycle Delayed signal , You can also rely on sampling at a certain time before the sampling event , To simulate the sampling requirements of the setup time , Ensure the reliability of sampling .

2.clocking Clock block

- Can be in interface In a statement clocking And the sampled clock signal are used for signal synchronization and sampling .

- clocking The block is based on the clock cycle to drive or sample the signal , bring testbench No longer worry about how to accurately and timely drive or sample the signal , Eliminate the signal competition problem .

// stay clock1 To drive and sample

clocking [email protected](posedge clock1);

// stay clock1 Before the rising edge 10ns Input sample it ,

// After 2ns Drive it out .

default input #10ns output #2ns

input ready, margin;

output data, valid;

endclocking

clocking Use

- clocking Blocks can not only be defined in interface in , It can also be defined in module and program in .

- clocking The signals listed in are not self-defined , It should be interface Or any other statement clocking Module defined by .

- clocking After declaring the name , It should be accompanied by the definition of default sampling events , namely "default input/output event". If there is no definition , Will default to the clocking Before the sampling event 1step Sample the input , After the sampling event #0 Drive the output .

- In addition to defining default sampling and driving events , You can also define the signal direction , Overwrite the default event with the new sampling event .

边栏推荐

- HMS Core机器学习服务实现同声传译,支持中英文互译和多种音色语音播报

- 网上股票开户安不安全?有谁知道呢

- Modal and modeless dialogs for QT

- 成员变量与局部变量的区别

- [untitled]

- JS get the height and width corresponding to the box model (window.getcomputedstyle, dom.getboundingclientrect)

- SPARQL learning notes of query, an rrdf query language

- Flexible layout (display:flex;) Attribute details

- Gif动图如何裁剪?收下这个图片在线裁剪工具

- Source code analysis of zeromq lockless queue

猜你喜欢

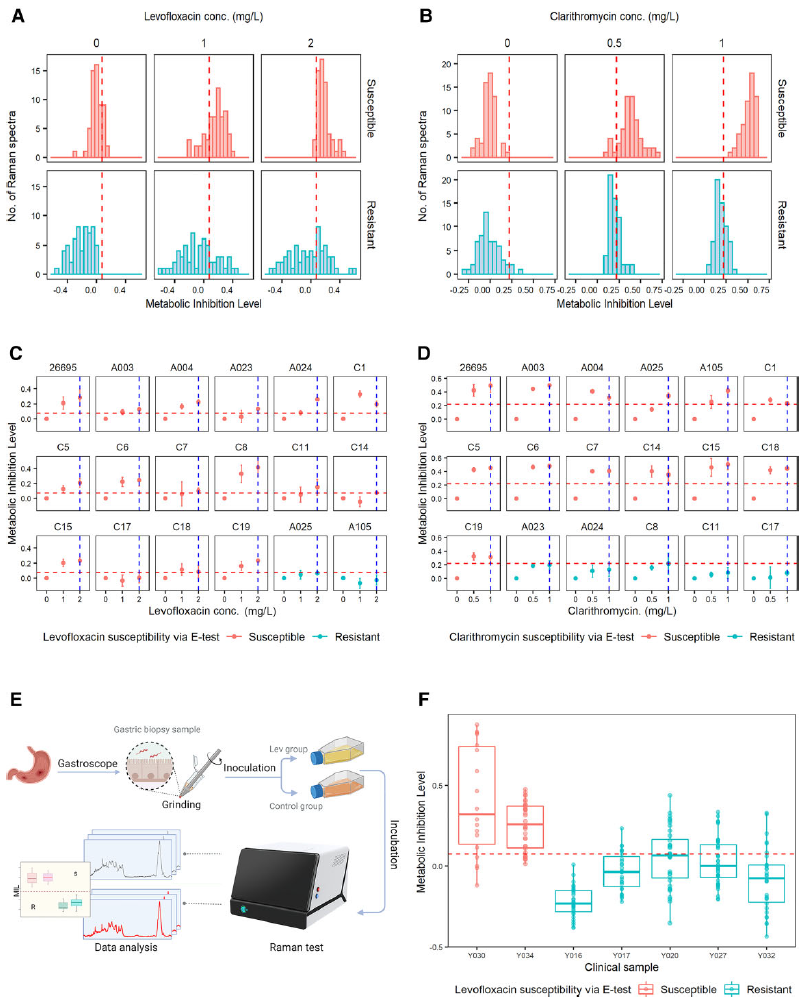

Clinical Chemistry | 张建中/徐健开发幽门螺杆菌单细胞精准诊疗技术

ffmpeg protocol concat 进行ts流合并视频的时间戳计算及其音画同步方式一点浅析

How to make GIF animation online? Try this GIF online production tool

How to combine multiple motion graphs into a GIF? Generate GIF animation pictures in three steps

One question per day,

重磅!国产 IDE 发布,由阿里研发,完全开源!(高性能+高定制性)

搭建极简GB28181 网守和网关服务器,建立AI推理和3d服务场景,然后开源代码(一)

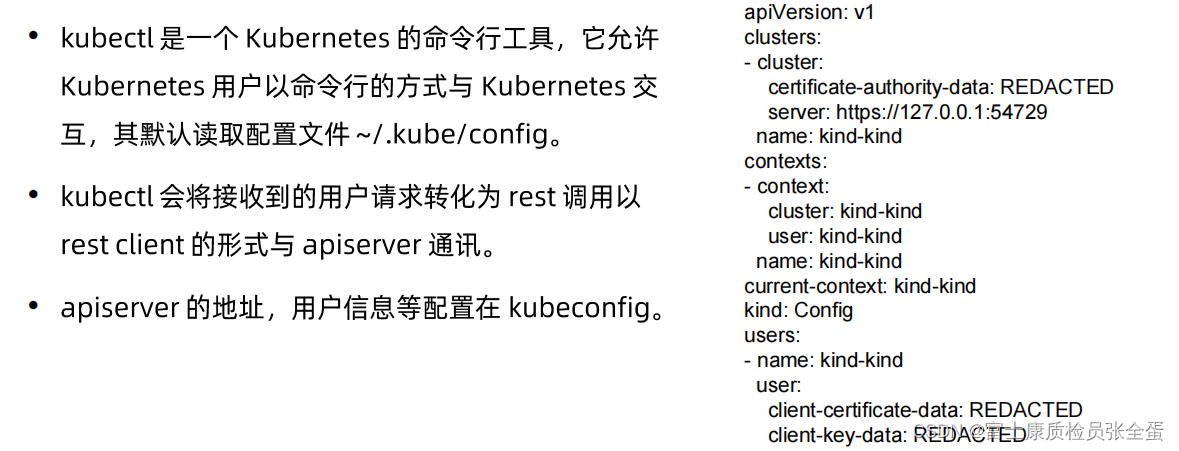

Kubernetes 理解kubectl/调试

定位position(5种方式)

From 408 to independent proposition, 211 to postgraduate entrance examination of Guizhou University

随机推荐

Application of TSDB in civil aircraft industry

Is it safe to open an online stock account? Who knows

Thymeleaf Usage Summary

Basic knowledge of pointer

从0到1完全掌握 XSS

2022年广东高考分数线出炉,一个几家欢喜几家愁

Is it normal to dig for money? Is it safe to open a stock account?

Custom instruction, mixing, routing, lifecycle

买卖股票的最佳时机

[deep learning] multi task learning of multiple datasets data sets missing labels

SPARQL learning notes of query, an rrdf query language

Review of arrays and pointers triggered by a topic

Daily question, Caesar code,

分饼干问题

Std:: vector minutes

Deconstruction assignment of variables

Source code analysis of zeromq lockless queue

JS recursion and while

Design and implementation of timer

Go语言Zap库Logger的定制化和封装使用详解