当前位置:网站首页>DDR SDRAM board design guide

DDR SDRAM board design guide

2022-07-24 18:49:00 【U.2 SSD】

DDR SDRAM Board Design Guide

The main topics are as follows :

- The termination scheme has an impact on the signal quality of the receiving end

- The output driving strength has an impact on the signal quality of the receiving end

- Load type affects signal integrity

The core goal : Understand termination types 、 Trade off between output drive strength and load type .

The key factors affecting the signal quality of the receiving end are as follows :

- Leveling and dynamic ODT

- Proper use of termination

- Output driver drive strength setting

- Loading at the receiver

- Layout guidelines

Leveling and Dynamic ODT

DDR3 and DDR4 SDRAM DIMMs, as specified by JEDEC, always use a fly-by topology for the

address, command, and clock signals.

Altera recommends that for full DDR3 or DDR4 SDRAM compatibility when using discrete

DDR3 or DDR4 SDRAM components, you should mimic the JEDEC DDR3 or DDR4 fly-by topology

on your custom printed circuit boards (PCB).

Read and Write Leveling

A major difference between DDR2 and DDR3/DDR4 SDRAM is the use of leveling.

In order to improve signal integrity and support higher frequency operation ,JEDEC The Association defines the clock , Command and address bus used fly-by Termination scheme .

read and write leveling stay DDR2 and DDR3 Differences exist , however DDR4 Of Leveling Technology and DDR3 be similar

fly-by The topology deliberately reduces the synchronous switching noise (SSN)

边栏推荐

- MySQL optimization series (2) -- InnoDB important parameter optimization

- Data model subclassing reference

- PCIe link initialization & Training

- 关于core文件

- Ionic4 learning notes 10 rotation map of an East Project

- Typora user manual

- Tree chain partition board

- 轻松学Pytorch-迁移学习实现表面缺陷检查

- Vsftpd2.3.4-端口渗透 6200 irc_3281_backdoor

- Nftscan and port3 have reached strategic cooperation in the field of NFT data

猜你喜欢

Inoic4 learning notes 2

QT - animation frame

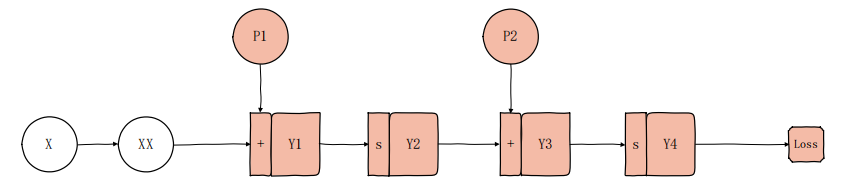

Understand dynamic calculation diagram, requires_ grad、zero_ grad

Create parent-child projects in clion (cmake tool) and introduce the method of third-party libraries

04-分布式资源管理系统YARN

Cf. bits and pieces (subset pressing DP + pruning)

Vsftpd2.3.4-端口渗透 6200 irc_3281_backdoor

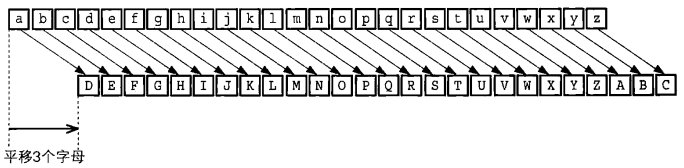

Cryptography knowledge - Introduction to encryption -1

Ionic4 learning notes 10 rotation map of an East Project

![[today in history] July 24: caldera v. Microsoft; Amd announced its acquisition of ATI; Google launches chromecast](/img/7d/7a01c8c6923077d6c201bf1ae02c8c.png)

[today in history] July 24: caldera v. Microsoft; Amd announced its acquisition of ATI; Google launches chromecast

随机推荐

MySQL optimization series (2) -- InnoDB important parameter optimization

New stage of investment

Typora user manual

【TkInter】布局管理和事件系统

OpenGL learning (V) modern OpenGL triangle rendering

The difference between KIB and MIB and KB and MB

Ionic4 learning notes 10 rotation map of an East Project

Eternal Blue ms17-010exp reappears

关于core文件

Namespace: cluster environment sharing and isolation

Crazy God redis notes 11

Generate publickey with der format public key and report an error

【微信小程序开发】自定义tabBar案例(定制消息99+小红心)

What are the benefits of knowledge management in enterprises?

Tcl/tk file operation

Nftscan and port3 have reached strategic cooperation in the field of NFT data

Cryptography knowledge - Introduction to encryption -1

狂神redis笔记11

Why is gradient the fastest changing direction of function

FPGA 20个例程篇:9.DDR3内存颗粒初始化写入并通过RS232读取(上)