当前位置:网站首页>Introduction to HLS programming

Introduction to HLS programming

2022-07-24 22:49:00 【Don't recognize Xueba】

Catalog

One 、HLS brief introduction

HLS It's a high-level comprehensive (High level Synthesis)

Yes, it will C perhaps c++ The language is compiled as FPGA Able to read and run RTL Level language

And VHDL perhaps verilog Comparison

advantage : Use high-level language to complete the functions expected to be realized on the hardware circuit , More abstract and easy to implement .

shortcoming : Although it is described in high-level language to realize the function on the hardware circuit , But there will be many restrictions , For example, functions such as dynamic memory allocation or defined disabling , There are also many shortcomings , For example, the optimization of loops is always a big problem .

HLS key technology

1、 Translate high-level languages into RTL circuit

2、 Cycle optimization , parallel processing

Two 、 beginner HLS Program ( Lighten up led The lamp )

( One ) Simulation

Environmental Science :xilinx20.2

The board : Z7-Lite7020

1、 New project

Select a definite function It's direct here next

add to c Simulation file ,testbench file ,next

Choose here xc7z020clg400-2, Corresponding Z7-Lite7020

New project completion page

2、 Add source file

Add header files in the same way

led.h Code

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#define CNT_MAX 100000000

//#define CNT_MAX 100

#define FLASH_FLAG CNT_MAX-2

typedef int led_t;

typedef int cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

The maximum count CNT_MAX 100000000 Is in 100M The number of counts required to count a second at the clock frequency FLASH_FLAG yes LED Flashing signs , When the count reaches this value

when ,LED change flash_led It is the definite function that the project needs to design

Subsequent optimization code

led.h

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#include "ap_int.h"

#define CNT_MAX 100000000

//#define CNT_MAX 100

#define FLASH_FLAG CNT_MAX-2

//typedef int led_t;

//typedef int cnt_t;

typedef ap_int<1>led_t;

typedef ap_int<32>cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

led.h Code

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

Variable i Count to FLASH_FLAG when led_o The state of

3、 add to c Simulation file

test_led.cpp Code

#include "led.h"

#include <stdio.h>

int main(){

led_t led_i=0x01;

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o , led_i);

led_i = led_o;

printf("shift_out is %d \n",(int)(led_o&0x01));

}

}

Subsequent optimization settings

4、 Conduct C Simulation and C comprehensive

choice flash_led As a top-level function

c Simulation

c The simulation results are consistent with expectations

c comprehensive

Results successful

Latency refer to , It takes time to design a circuit to complete a task

Interval It refers to the time interval between two tasks

FF Number of triggers :62

LUT Number of lookup tables :105

Other generated results are not concerned for the time being ( Because I really don't understand , This project does not need attention )

Co simulation

and c The simulation results are consistent

( Two ) burn

1、 export HLS Project generated IP nucleus

Do not change , direct OK

Derived IP Nuclear will be Solution This folder can be found

vivado Project import ip

open vivado, New project

add to ip

Locate the solution

Apply after adding successfully

Add success

stay IP Catalog Selected by HLS Generated IP, Double click and generate the IP

Add a new file to the project , Used to complete this experiment

led.v Is what the code will generate HLS IP Example into the project

//

// Company:

// Engineer:

//

// Create Date: 2021/05/22 14:40:22

// Design Name:

// Module Name: led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

`timescale 1ns / 1ps

module flash_led(

input wire clk ,

input wire rst_n ,

output wire led_o

);

wire rst ;// Synchronous reset

wire ap_ready ;// Now you can receive the next data

reg ap_start ;//IP start-up

reg led_i_vld ;// The input data is valid

wire led_o_vld ;

reg led_i ;// Input led The signal

wire led_o_r ;

wire ap_done ;

wire ap_idle ;

reg [1:0] delay_cnt ;

assign rst = ~rst_n ;

assign led_o = led_o_r ;

//----------------delay_cnt------------------

always @(posedge clk) begin

if (rst==1'b1) begin

delay_cnt <= 'd0;

end

else if(delay_cnt[1]==1'b0) begin

delay_cnt <= delay_cnt + 1'b1;

end

end

//----------------ap_start------------------

always @(posedge clk) begin

if (rst==1'b1) begin

ap_start <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

ap_start <= 1'b1;

end

end

//----------------led_i_vld------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i_vld <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

led_i_vld <= 1'b1;

end

end

//----------------ap_i------------------

always @(posedge clk) begin

if (rst==1'b1) begin

led_i <= 1'b0;

end

else if(led_o_vld==1'b1)begin

led_i <= led_o_r ;

end

end

flash_led_0 inst_flash_led (

.led_o_ap_vld(led_o_vld), // output wire led_o_V_ap_vld

.led_i_ap_vld(led_i_vld), // input wire led_i_V_ap_vld

.ap_clk(clk), // input wire ap_clk

.ap_rst(rst), // input wire ap_rst

.ap_start(ap_start), // input wire ap_start

.ap_done(ap_done), // output wire ap_done

.ap_idle(ap_idle), // output wire ap_idle

.ap_ready(ap_ready), // output wire ap_ready

.led_o_V(led_o_r), // output wire [0 : 0] led_o_V

.led_i_V(led_i) // input wire [0 : 0] led_i_V

);

endmodule

The next step is to add constraint files

top_pin.xdc

##############LED define##################

set_property PACKAGE_PIN P15 [get_ports {

led_o}]

set_property IOSTANDARD LVCMOS33 [get_ports {

led_o}]

##############Reset define##################

set_property PACKAGE_PIN P16 [get_ports {

rst_n}]

set_property IOSTANDARD LVCMOS33 [get_ports {

rst_n}]

##############50M CLK define##################

create_clock -period 20.000 -name clk -waveform {

0.000 10.000} [get_ports clk]

set_property PACKAGE_PIN N18 [get_ports {

clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {

clk}]

add to ila Observe the intermediate process

This ip Corresponding .v In the document

Generate bit Streaming files

Open the hardware burning page after completion

Connect the board to the computer , Click auto connect to automatically find the connected board

Right click on the Program Device

Here, the burnable program will be automatically filled , Click on Program You can burn it

result

The video is too large I can't get it

summary : There are still many operations that I don't understand , But after the general completion , To use xilinx Of hls Have a certain understanding of the routine , It won't be like being completely blind before doing it , As for the principle part , Only a few understand , Most of them are what they should be .

Source of learning : Microphase board tutorial , Including video ,pdf etc.

边栏推荐

- Network Security Learning (IV) user and group management, NTFS

- How static code analysis works

- 【数据库学习】Redis 解析器&&单线程&&模型

- P3201 [hnoi2009] dream pudding heuristic merge

- 《ArchSummit:珍爱微服务底层框架演进》

- The size of STM32 stack

- burp从溯源到反制思路

- Network Security Learning (III) basic DOS commands

- Things to study

- 由斐波那契数列引述到矩阵快速幂技巧

猜你喜欢

![[database learning] redis parser & single thread & Model](/img/70/c84eb02d45e35fede4dd1b1ff04392.png)

[database learning] redis parser & single thread & Model

![[1184. Distance between bus stops]](/img/dd/3437e6a14ac02dac01c78b372a5498.png)

[1184. Distance between bus stops]

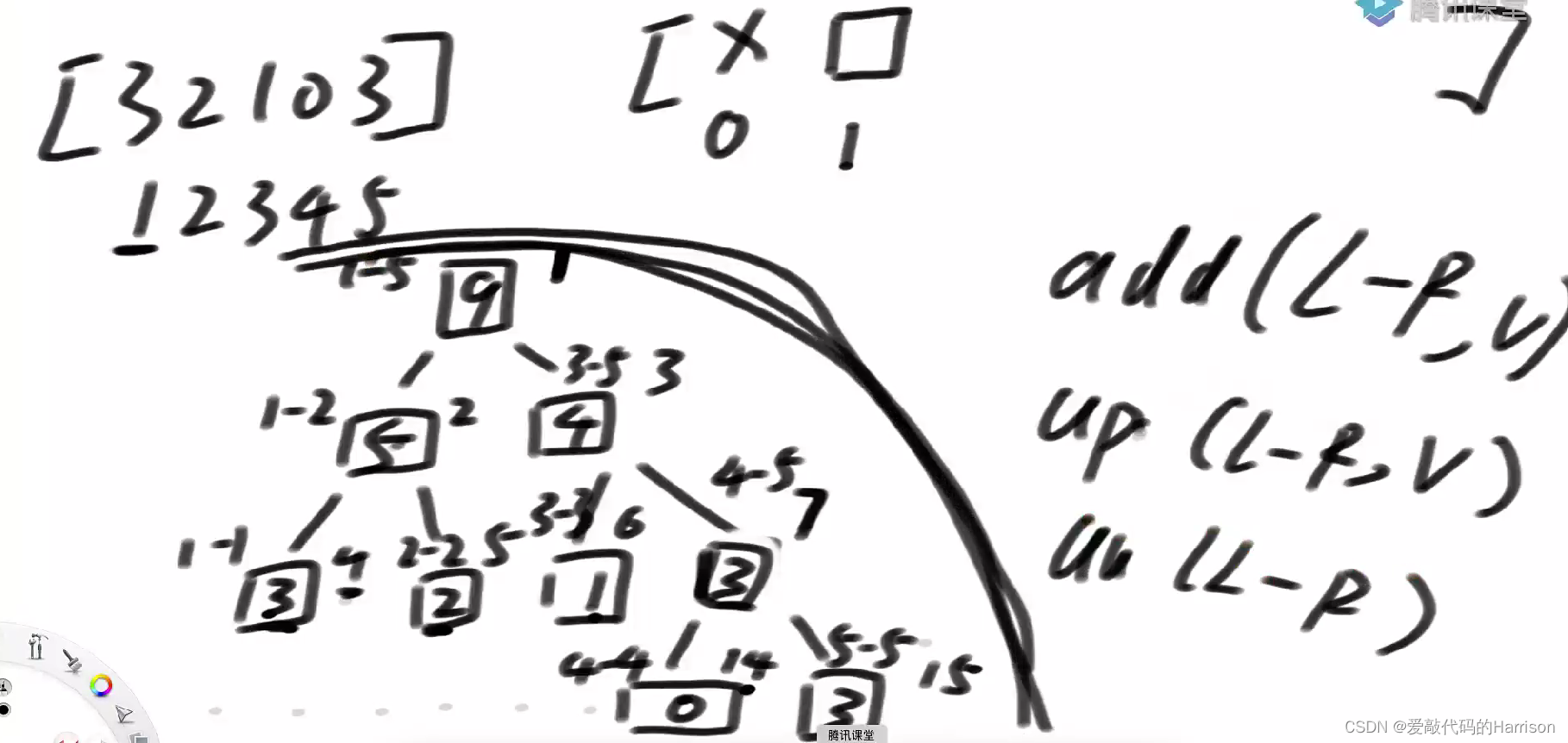

Segment tree,,

Oracle中实现对指定数据分组且获取重复次数

【数据库学习】Redis 解析器&&单线程&&模型

把字符串转换成整数与不要二

Okaleido tiger NFT即将登录Binance NFT平台,后市持续看好

基于Verilog HDL的数字秒表

From violent recursion to dynamic programming, memory search

Some analysis of slow MySQL query

随机推荐

Which is the best interface documentation tool at home and abroad?

EL & JSTL: JSTL summary

用VS Code搞Qt6:编译源代码与基本配置

ASP. Net core 6.0 data validation based on model validation

Time series data in industrial Internet of things

Joint search set structure

Morris traversal

Boundary extraction of PCL point cloud processing (58)

CA证书制作实战

【零基础】php代码审计之sql注入

GB、MB、KB分别是什么意思。大小分别是多少

WPF uses pathgeometry to draw the hour hand and minute hand

The specified data is grouped and the number of repetitions is obtained in Oracle

Glidemodule appglidemodule and generated API details

Org.json Jsonexception: what about no value for value

Trinitycore worldofwarcraft server - registration website

HLS编程入门

物联网平台返回数据解析时遇到org.json.JSONException: No value for Value怎么办

[zero basis] SQL injection for PHP code audit

ASP.NET Core 6.0 基于模型验证的数据验证