当前位置:网站首页>Imx8qxp DMA resources and usage (unfinished)

Imx8qxp DMA resources and usage (unfinished)

2022-06-27 08:31:00 【Wangerche】

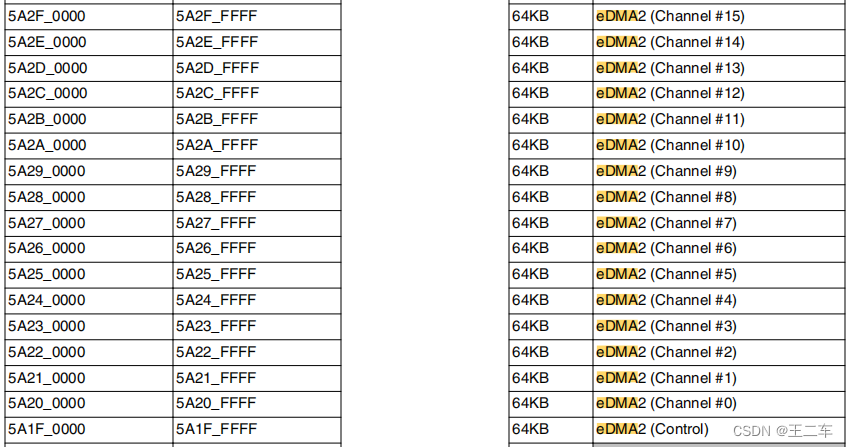

Have 4 individual edma(Enhanced Direct Memory Access) Enhanced direct memory access ,

4 individual edma All in all 96 Channels , 2 There are 32 and 16 Channels ,

With spi For example , You can use dma passageway , Configuration register

dts To configure , Yes TX and RX Configuration of , There are two configuration methods :

lpspi3: [email protected] {

compatible = "fsl,imx7ulp-spi";

reg = <0x0 0x5a030000 0x0 0x10000>;

interrupts = <GIC_SPI 219 IRQ_TYPE_LEVEL_HIGH>;

interrupt-parent = <&gic>;

clocks = <&clk IMX8QXP_SPI3_CLK>,

<&clk IMX8QXP_SPI3_IPG_CLK>;

clock-names = "per", "ipg";

assigned-clocks = <&clk IMX8QXP_SPI3_CLK>;

assigned-clock-rates = <20000000>;

power-domains = <&pd_dma2_chan7>;

dma-names = "tx","rx";

dmas = <&edma2 7 0 0>, <&edma2 6 0 1>;

status = "disabled";

};

pd_dma_lpspi3: PD_DMA_SPI_3 {

reg = <SC_R_SPI_3>;

#power-domain-cells = <0>;

power-domains = <&pd_dma>;

wakeup-irq = <339>;

pd_dma2_chan6: PD_LPSPI3_RX {

reg = <SC_R_DMA_2_CH6>;

power-domains =<&pd_dma_lpspi3>;

#power-domain-cells = <0>;

#address-cells = <1>;

#size-cells = <0>;

pd_dma2_chan7: PD_LPSPI3_TX {

reg = <SC_R_DMA_2_CH7>;

power-domains =<&pd_dma2_chan6>;

#power-domain-cells = <0>;

#address-cells = <1>;

#size-cells = <0>;

};

};

};lpspi3: [email protected] {

compatible = "fsl,imx7ulp-spi";

reg = <0x0 0x5a030000 0x0 0x10000>;

interrupts = <GIC_SPI 219 IRQ_TYPE_LEVEL_HIGH>;

interrupt-parent = <&gic>;

clocks = <&clk IMX8QXP_SPI3_CLK>,

<&clk IMX8QXP_SPI3_IPG_CLK>;

clock-names = "per", "ipg";

assigned-clocks = <&clk IMX8QXP_SPI3_CLK>;

assigned-clock-rates = <20000000>;

power-domains = <&pd_dma_lpspi3>;

dma-names = "tx","rx";

dmas = <&edma2 7 0 0>, <&edma2 6 0 1>;

status = "okay";

};

pd_dma_lpspi3: PD_DMA_SPI_3 {

reg = <SC_R_SPI_3>;

#power-domain-cells = <0>;

power-domains = <&pd_dma>;

};

edma 0 To 3 The difference between :

edma3 16 individual ,edma2 32 individual ( be used for SPI and UART),edma1 16 individual ,edma0 32 individual (SAI).

edma2: [email protected] {

compatible = "fsl,imx8qm-edma";

reg = <0x0 0x5a200000 0x0 0x10000>, /* channel0 LPSPI0 rx */

<0x0 0x5a210000 0x0 0x10000>, /* channel1 LPSPI0 tx */

<0x0 0x5a220000 0x0 0x10000>, /* channel2 LPSPI1 rx */

<0x0 0x5a230000 0x0 0x10000>, /* channel3 LPSPI1 tx */

<0x0 0x5a240000 0x0 0x10000>, /* channel4 LPSPI2 rx */

<0x0 0x5a250000 0x0 0x10000>, /* channel5 LPSPI2 tx */

<0x0 0x5a260000 0x0 0x10000>, /* channel6 LPSPI3 rx */

<0x0 0x5a270000 0x0 0x10000>, /* channel7 LPSPI3 tx */

<0x0 0x5a280000 0x0 0x10000>, /* channel8 UART0 rx */

<0x0 0x5a290000 0x0 0x10000>, /* channel9 UART0 tx */

<0x0 0x5a2a0000 0x0 0x10000>, /* channel10 UART1 rx */

<0x0 0x5a2b0000 0x0 0x10000>, /* channel11 UART1 tx */

<0x0 0x5a2c0000 0x0 0x10000>, /* channel12 UART2 rx */

<0x0 0x5a2d0000 0x0 0x10000>, /* channel13 UART2 tx */

<0x0 0x5a2e0000 0x0 0x10000>, /* channel14 UART3 rx */

<0x0 0x5a2f0000 0x0 0x10000>; /* channel15 UART3 tx */

#dma-cells = <3>;

dma-channels = <16>;

interrupts = <GIC_SPI 416 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 417 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 418 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 419 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 420 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 421 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 422 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 423 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 434 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 435 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 436 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 437 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 438 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 439 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 440 IRQ_TYPE_LEVEL_HIGH>,

<GIC_SPI 441 IRQ_TYPE_LEVEL_HIGH>;

interrupt-names = "edma2-chan0-rx", "edma2-chan1-tx",

"edma2-chan2-rx", "edma2-chan3-tx",

"edma2-chan4-rx", "edma2-chan5-tx",

"edma2-chan6-rx", "edma2-chan7-tx",

"edma2-chan8-rx", "edma2-chan9-tx",

"edma2-chan10-rx", "edma2-chan11-tx",

"edma2-chan12-rx", "edma2-chan13-tx",

"edma2-chan14-rx", "edma2-chan15-tx";

pdomains = <&pd_dma2_chan0>, <&pd_dma2_chan1>,/* lpspi0 */

<&pd_dma2_chan2>, <&pd_dma2_chan3>,/* lpspi1 */

<&pd_dma2_chan4>, <&pd_dma2_chan5>,/* lpspi2 */

<&pd_dma2_chan6>, <&pd_dma2_chan7>,/* lpspi3 */

<&pd_dma2_chan8>, <&pd_dma2_chan9>,/* UART0 */

<&pd_dma2_chan10>, <&pd_dma2_chan11>,/* UART1 */

<&pd_dma2_chan12>, <&pd_dma2_chan13>,/* UART2 */

<&pd_dma2_chan14>, <&pd_dma2_chan15>;/* UART3 */

status = "okay";

};

spi dma Code flow

fsl_lpspi_probe

fsl_lpspi_dma_init

controller->transfer_one = fsl_lpspi_transfer_one;

fsl_lpspi_dma_init

controller->dma_tx = dma_request_slave_channel_reason(dev, "tx");

controller->dma_rx = dma_request_slave_channel_reason(dev, "rx");

controller->can_dma = fsl_lpspi_can_dma;

controller->max_dma_len = FSL_LPSPI_MAX_EDMA_BYTES; ((1 << 15) - 1)

fsl_lpspi_transfer_one

fsl_lpspi_setup_transfer

if (fsl_lpspi_can_dma(controller, spi, t))

fsl_lpspi->usedma = 1;

else

fsl_lpspi->usedma = 0;

fsl_lpspi_can_dma

bytes_per_word = fsl_lpspi_bytes_per_word(transfer->bits_per_word);

if (bytes_per_word != 1 && bytes_per_word != 2 && bytes_per_word != 4)【8/16/32 bits_per_word Send using DMA, The range should be 8~32bit】

return false;

fsl_lpspi_config

if (fsl_lpspi->usedma)

temp = DER_TDDE | DER_RDDE;

writel(temp, fsl_lpspi->base + IMX7ULP_DER);

Another important member is bits_per_word. This member specifies the word length for each read and write , The unit is bit . Although most of SPI The word length of the interface is 8 perhaps 16, There will still be some special examples . It should be noted that , If this member is zero , By default 8 As word length .

fsl_lpspi_set_cmd

Set up bpw,mode

if (fsl_lpspi->usedma)

ret = fsl_lpspi_dma_transfer(controller, fsl_lpspi, t);

else

ret = fsl_lpspi_pio_transfer(controller, t);

fsl_lpspi_dma_transfer

fsl_lpspi_dma_configure

buswidth = DMA_SLAVE_BUSWIDTH_1_BYTE;

tx.direction = DMA_MEM_TO_DEV;

tx.dst_addr = fsl_lpspi->base_phys + IMX7ULP_TDR;

tx.dst_addr_width = buswidth;

tx.dst_maxburst = 1;

ret = dmaengine_slave_config(controller->dma_tx, &tx); doubt :

1、 You can choose to use... To send data DMA The way , Receiving data is a situation of using interrupts +dma The way ?

DMA test :

1、 send data , Set up bits_per_word=8/16/32, see cpu Usage rate , Set up 12/20 Compare the total system time sent , Print with inner kernel function .

2、 receive data , The same test .

边栏推荐

- ArrayList和LinkedList的区别

- MySQL锁详解

- (原创)自定义Drawable

- [batch dos-cmd command - summary and summary] - parameters%0,%1,%2,%[0-9],%0-9 in the batch command and batch command parameter position switching command shift, operator% usage in the DOS command

- i=i++;

- Lvgl description 3 about the use of lvgl Guide

- lvgl使用demo及说明2

- 第十一章 信号(一)- 概念

- RockerMQ消息发送模式

- ServletConfig与ServletContext

猜你喜欢

0号进程,1号进程,2号进程

粗读DS-TransUNet: Dual Swin Transformer U-Net for Medical Image Segmentation

Enumeration? Constructor? Interview demo

(原创)自定义Drawable

Code source AQS sous - jacent pour la programmation simultanée juc

oracle怎样将字符串转为多行

【mysql篇-基础篇】通用语法1

DataV轮播表组件dv-scroll-board宽度问题

MySQL index details

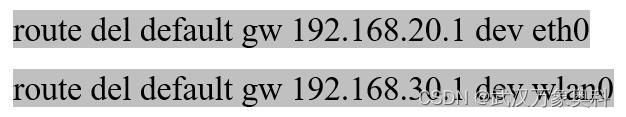

多网络设备存在时,如何配置其上网优先级?

随机推荐

JVM层次上的对象的创建过程和内存布局

[notes on c++ primer] Chapter 3 string, vector and array

[original] typescript string UTF-8 encoding and decoding

orthofinder直系同源蛋白分析及结果处理

Lvgl GUI guide porting code to stm32

Zabbix部署说明(Server+Win客户端+交换机(H3C))

All tutor information on one page

Chapter 11 signal (I) - concept

100% understanding of 5 IO models

Redis installation under Linux

Mapping of Taobao virtual product store opening tutorial

Eight misunderstandings, broken one by one (final): the cloud is difficult to expand, the customization is poor, and the administrator will lose control?

Ready to migrate to the cloud? Please accept this list of migration steps

[13. number and bit operation of 1 in binary]

C# 解决使用SQLite 的相对路径问题

参考 | Win11 开启热点之后电脑不能上网

[batch dos-cmd command - summary and summary] - output / display command - echo

[paper reading] internally semi supervised methods

Filter filter

直接修改/etc/crontab 文件内容,定时任务不生效