当前位置:网站首页>quartus調用&設計D觸發器——仿真&時序波驗證

quartus調用&設計D觸發器——仿真&時序波驗證

2022-06-23 13:35:00 【小小怪༻】

quartus調用&設計D觸發器——仿真&時序波驗證

目錄

1、 在 Quartus-II 中自己用門電路設計一個D觸發器,並進行仿真,時序波形驗證;

2、在 Quartus-II 中直接調用一個D觸發器電路,進行仿真,時序波形驗證,與2做比較;

3、在 Quartus-II用Verilog語言寫一個D觸發器,進行仿真驗證

一、認識D觸發器

D觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種

時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。

D觸發器在時鐘脈沖CP的前沿(正跳變0→1)發生翻轉,觸發器的次態取决於CP的脈沖上昇沿到來之前D端的狀態,即次態=D。因此,它具有置0、置1兩種功能。由於在CP=1期間電路具有維持阻塞作用,所以在CP=1期間,D端的數據狀態變化,不會影響觸發器的輸出狀態。

D觸發器應用很廣,可用做數字信號的寄存,移比特寄存,分頻和波形發生器等。

1、結構

D觸發器(data flip-flop或delay flip-flop)由4個與非門組成,其中G1和G2構成基本RS觸發器。電平觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP高電平期間輸入端出現幹擾信號,那麼就有可能使觸發器的狀態出錯。而邊沿觸發器允許在CP觸發沿來到前一瞬間加入輸入信號。這樣,輸入端受幹擾的時間大大縮短,受幹擾的可能性就降低了。邊沿D觸發器也稱為維持-阻塞邊沿D觸發器。邊沿D觸發器可由兩個D觸發器串聯而成,但第一個D觸發器的CP需要用非門反向。

2、特征

功能錶

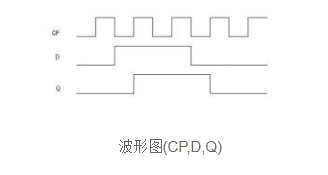

時序圖

這裏就是對D觸發器的一個簡單介紹,有關更多D觸發器的認識,大家可以參考下面鏈接;

D觸發器.

二、設計D觸發器及時序驗證

1、創建工程

file—>new project wizard

編輯工程名稱,後面點擊next

選擇合適的芯片及其系列

直接next

工程創建完成,點擊finish

2、創建方框文件

點擊new

選擇紅色方框的署名

按圖示選擇

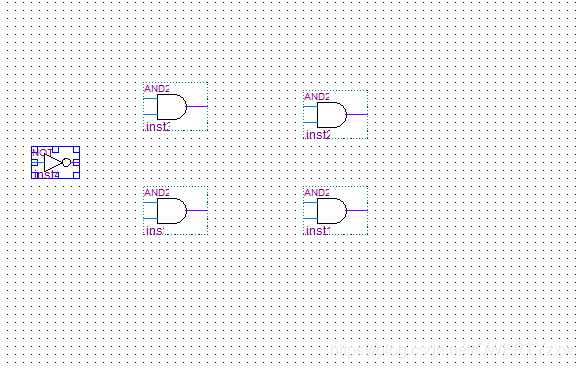

選擇nand2,兩個輸入的與非門,依次添加4個nand2和一個非門not

添加完成後如圖

選擇連線工具

連線效果如圖(雙擊鼠標可以更改引脚名稱)

保存電路圖

3、編譯原理圖文件

編譯電路圖

編譯界面

rtl viewer,查看硬件電路圖

電路圖

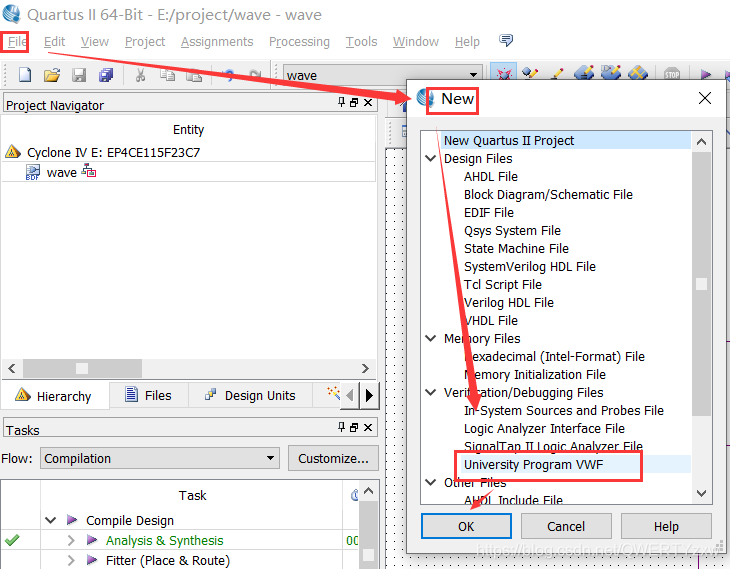

4、創建vwm波形文件

選擇圖示vwm

操作如圖

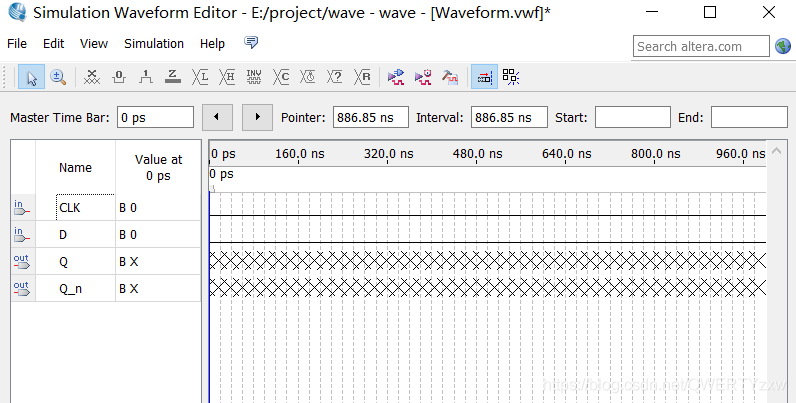

添加node or bus

效果展示

編輯輸入信號clk,產生時鐘信號

鼠標選擇D,Q信號Q_n,進行編輯(鼠標左鍵選中 雙擊改值)

5、時序波形仿真

編譯

出現報錯

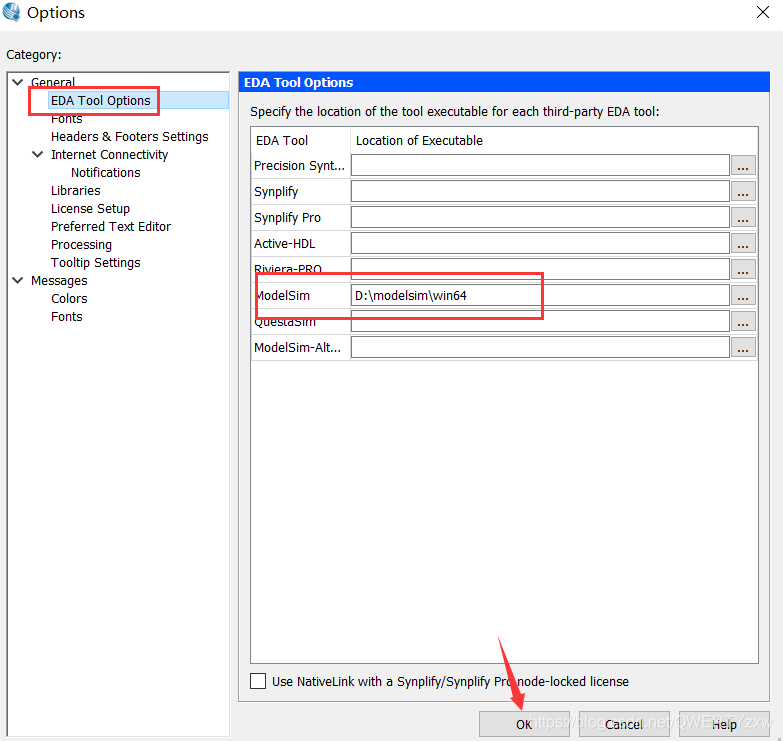

連接modelsim

報錯解决方法

結果如圖

仿真結果

三、調用D觸發器及時序驗證

1、創建方框文件

創建工程方法同上

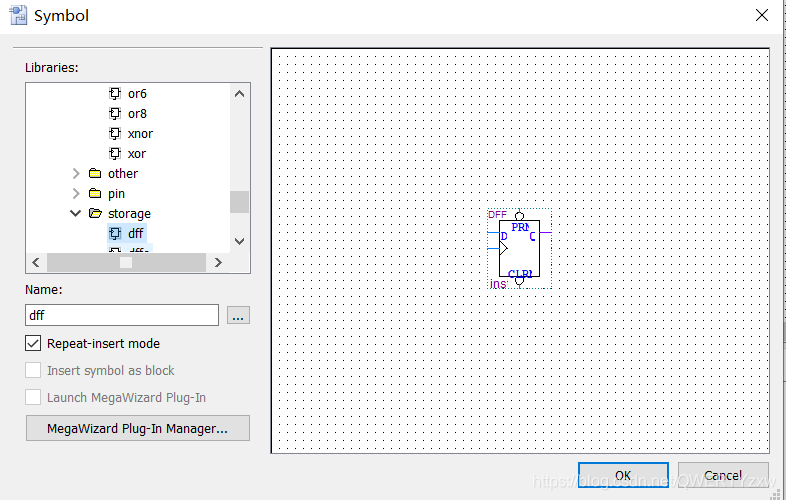

調用D觸發器

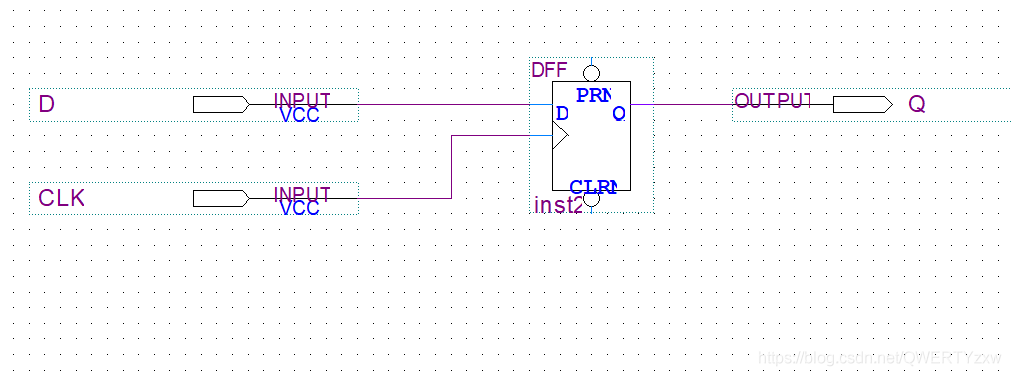

連線補引脚,效果如圖(Ctrl+鼠標滾輪可以對觸發器引脚等進行縮放)

2、編譯原理圖

查看硬件圖

編譯

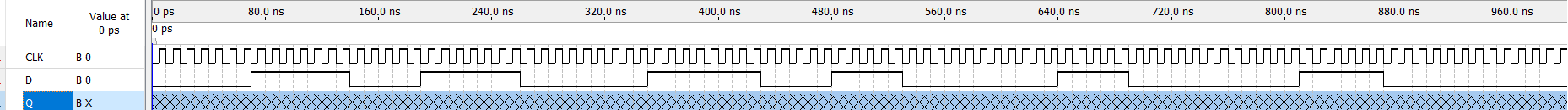

3、創建vwm波形文件及仿真

波形

時序仿真結果

四、verilog語言實現D觸發器及時序驗證

1、編寫verilog文件

首先創建工程,方法同上

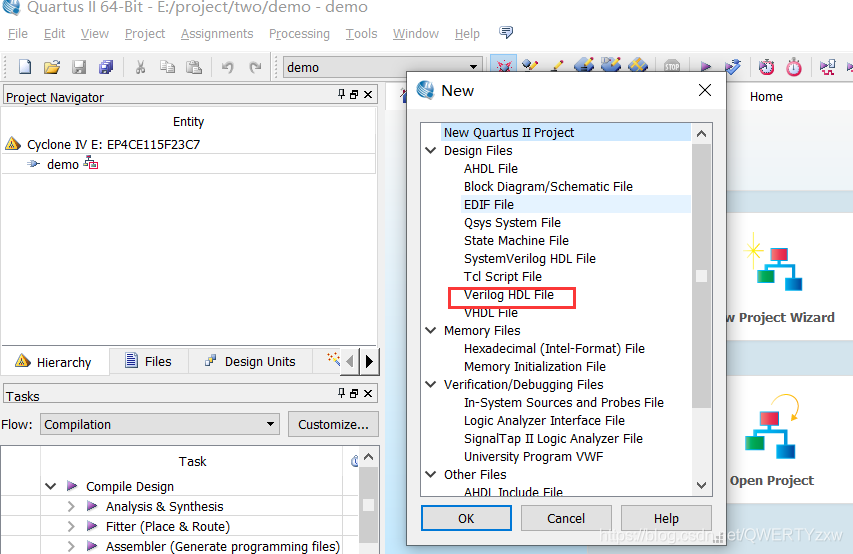

創建Verilog文件,點擊file—new

粘貼如下代碼

//demo是文件名

module demo(d,clk,q);

input d;

input clk;

output q;

reg q;

always @ (posedge clk)//我們用正的時鐘沿做它的敏感信號

begin

q <= d;//上昇沿有效的時候,把d捕獲到q

end

endmodule

保存並編譯

2、查看生成的電路圖

3、測試時序仿真

代碼如下

//測試代碼

`timescale 1ns / 1ns

module demo_tb;

reg clk,d;

wire q;

demo u1(.d(d),.clk(clk),.q(q));

initial

begin

clk = 1;

d <= 0;

forever

begin

#60 d <= 1;//人為生成毛刺

#22 d <= 0;

#2 d <= 1;

#2 d <= 0;

#16 d <= 0;//維持16ns的低電平,然後讓它做周期性的循環

end

end

always #20 clk <= ~clk;//半周期為20ns,全周期為40ns的一個信號

endmodule

保存並編譯

仿真效果圖

五、總結與參考資料

1、總結

D觸發器及時序仿真的過程,可以發現D觸發器的基本功能是在複比特信號為1的時候,CLK的上昇沿會引起Q值的變化。由此,可以得出次態方程為 Q n + 1 = D

2、參考資料

Quartus II自帶仿真工具的使用.

Quartus-II輸入原理圖及仿真步驟.docx.

Quartus-II13.1三種方式實現D觸發器及時序仿真.

边栏推荐

- 2-optical-2-electric cascaded optical fiber transceiver Gigabit 2-optical-2-electric optical fiber transceiver Mini embedded industrial mine intrinsic safety optical fiber transceiver

- What is the reason why maxcompute is sometimes particularly slow to execute SQL queries

- Architecture design methods in technical practice

- 16 channel HD-SDI optical transceiver multi channel HD-SDI HD video optical transceiver 16 channel 3g-sdi HD audio video optical transceiver

- 2022软科大学专业排名出炉!西电AI专业排名超清北,南大蝉联全国第一 !

- LM05丨曾经的VIX(二代产品)

- Loss, duplication and backlog of message queues

- Esp32-c3 introductory tutorial problem ⑦ - fatal error: ESP_ Bt.h: no such file or directory ESP not found_ bt.h

- How do the top ten securities firms open accounts? Is online account opening safe?

- Androd Gradle模块依赖替换如何使用

猜你喜欢

AGCO AI frontier promotion (6.23)

AAIG看全球6月刊(上)发布|AI人格真的觉醒了吗?NLP哪个细分方向最具社会价值?Get新观点新启发~

Quickly understand the commonly used asymmetric encryption algorithm, and no longer have to worry about the interviewer's thorough inquiry

Homekit supports the matter protocol. What does this imply?

64 channel telephone +2-channel Gigabit Ethernet 64 channel PCM telephone optical transceiver voice telephone to optical fiber

2-optical-2-electric cascaded optical fiber transceiver Gigabit 2-optical-2-electric optical fiber transceiver Mini embedded industrial mine intrinsic safety optical fiber transceiver

Germancreditdata of dataset: a detailed introduction to the introduction, download and use of germancreditdata dataset

逆向调试入门-了解PE结构文件

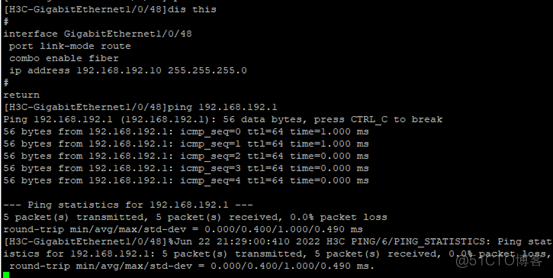

Configure SSH Remote Login for H3C switch

有向图D和E

随机推荐

Go write file permission WriteFile (filename, data, 0644)?

Develop a powerful tool for increasing efficiency - vscode plug-in sharing in 2022

Is it safe for flush to open an account online? What should we pay attention to

One way linked list implementation -- counting

HomeKit支持matter协议,这背后将寓意着什么?

First exposure! The only Alibaba cloud native security panorama behind the highest level in the whole domain

Cifar announces the second stage pan Canadian AI strategy

When did the redo log under InnoDB in mysql start to perform check point disk dropping?

互联网技术发展内卷后的出路——iVX的诞生

How to solve the task cache compilation problem caused by gradle build cache

2022软科大学专业排名出炉!西电AI专业排名超清北,南大蝉联全国第一 !

Esp32-c3 introductory tutorial problem ⑦ - fatal error: ESP_ Bt.h: no such file or directory ESP not found_ bt.h

"Four highs" of data midrange stability | startdt Tech Lab 18

R language uses the multinom function of NNET package to build a disordered multi classification logistic regression model, uses regression coefficients and their standard errors to calculate the valu

在线文本过滤小于指定长度工具

首次曝光!唯一全域最高等级背后的阿里云云原生安全全景图

16 channel HD-SDI optical transceiver multi channel HD-SDI HD video optical transceiver 16 channel 3g-sdi HD audio video optical transceiver

The way out after the development of Internet technology -- the birth of IVX

Hanyuan high tech new generation green energy-saving Ethernet access industrial switch high efficiency energy-saving Gigabit Industrial Ethernet switch

Strengthen the sense of responsibility and bottom line thinking to build a "safety dike" for flood fighting and rescue