当前位置:网站首页>Verilog syntax explanation

Verilog syntax explanation

2022-06-23 07:03:00 【Slag Ye】

Module composition :

Port specification : The interface type declared by the module , Mainly for input and output

data type :net Network type (wire),variable type (reg and integer)

In a module , stay initial and always in , The assigned variable must be variable type (reg and integer)

assign、 Module call 、 The output signal called by the door element is wire type

Define symbolic constants :parameter wid=18;

reg[3:0] c; // The seat width is 4 Register vector of

reg c[4:0]; // Capacity of 5 The memory of

reg[3:0] c[4:0]; // The word is 4, Capacity of 5 The memory of

==: The two operands involved in the comparison are equal bit by bit , Result only , If you have any x or z, The result is x

===: The unsteady state or high resistance state also needs to be consistent to be true

>>>: Count right

>>: Logical shift right

Conditional operator :signal=condition?true_expression:false_expression;

One way left a={a,count};// reg[7:0] a Is a shift memory ; count Is the data to be stored , Can be multiple

One way shift right a={count,a[3:1]};

Cycle moves to the right a={a[0],a[3:1]};// Be careful Cycle moves to the right 1 position , Shift data is filled in high order , The lower splicing part needs to be cut , Otherwise, the high bit cannot be stored in the sequence

Cyclic shift to the left a={a,a[3]}. Move left 1 position , Shift data is filled in the lowest bit , It can be cut off automatically when assigning values .

Procedure statements and block statements :

initial: Used in simulation code , Only once

1.begin-end, Represents the boundary of the code block , Where the code is a serial relationship , Execute in sequence , Time accumulates in one direction

initial

begin

#4 x=0;//(1)

#8 y=1;//(2)

end

In the above code , Delay... First 4, Further delay 8, Total delay 12 A unit of

2.fork-join, Code boundaries , The code belongs to the parallel relationship , At the same time

initial

fork

#4 x=0;

#8 y=1;

join

In the above code , At the same time , Delay four time units and delay 8 Execute respectively after time units , Attack delay 8 Time units

always: It can be used in comprehensive code , It can also be used in simulation code

always Generally speaking, it is related to begin-end Use it together , As long as the trigger conditions are met , Will always carry out .

always Format of statement :

always @(< Sensitive signal expression event-expression>)

begin// Process assignment

//if-else,case,casex,casez Select statement

//while,repeat,for loop

//task,function call

// Other statements

end“always” Procedure statements are usually with trigger conditions , The trigger condition is written in the sensitive signal expression , Only when the trigger conditions are met , “begin-end” Block statements can be executed .

[email protected](a), When a change , perform

[email protected](c,d), When c or d change , perform

[email protected](*), Represents all drive signals

Sequential logic always:

Use the edge to trigger ,posedge Rising edge ,negedge Falling edge

If in temporal logic , The clock clk, Can make ( control ) The signal reset、load

[email protected](posedge clk)//reset、load Synchronous signal

[email protected](posedge clk,posedge reset)//reset asynchronous ( high ),load Sync

[email protected](posedge clk,posedge reset,negedge load)

//reset asynchronous ( high )、load asynchronous ( low )

Assignment statement (assign、=、<=)

assign It belongs to continuous assignment statement

assign c=ab+cd Equivalent to assign c= (a&b)|(c&d)

c The data type is wire type

Block assignment “=”: Can be used for assign assignment , It can also be used for always sentence , Follow the steps

[email protected](posedge clk)

begin a=b;// The statement ends “;”,b The value of will override a

c=a;// Execute this sentence after the execution of the previous sentence

end

Code execution finished :c==a==b, Step by step

Nonblocking assignment “<=”: It can only be used for always In the sentence , Commonly used in temporal logic

[email protected](posedge clk)

begin

a<=b;// The sentence is finished ,b Does not cover a

c<=a;// The sentence is finished ,a Does not cover c

end// Fast statement terminator encountered , Change two sentences above At the same time

Code execution finished :b Cover a At the same time ,a Cover b, therefore c What is preserved in is a, No b;a What is preserved in is b. therefore a And b Same as ,c And a Same as , but b and c Not necessarily the same .

case The conditions in the structure are determined as “===”, Must be equal bit by bit

Degree of rigour :case>casez( Ignore z Corresponding bit )>casex( Ignore z、x Corresponding bit )

Loop statement :for It can be integrated into circuits and used for simulation ,forever、repeat、while Only for simulation

repeat(10) #5 clk=~clk; // loop 10 Time

forever #5 clk=~clk; // The cycle never stops

while(i<10)i=i+1; // loop 10 Time

Mission (task) And functions (function)

task ceshi;

On mission (task) There is no parameter list in

[email protected](....)

c=ceshi(a0,b0)*5+20;

Mission call : Only in intial perhaps always In process block , Independent idiom sentence

[email protected](*)

begin

ceshi(a0,b0,c0);

end

// Be careful c0 Assigned in the process block , So it is reg/integer type .Definition of function : Five parameter list , There is a return data bit width

function[1:0] ceshi;

Functional call : Can participate assign sentence :assign c=ceshi(a0,b0)+10;

You can also call... In a procedure block

[email protected](....)

c=ceshi(a0,b0)*5+20;

assign sentence 、 Module call 、always Fast process 、 There is a concurrent relationship between the calls of gate elements , Cannot nest

always In block ,begin--end The code in is assigned with blocking =, Statements are sequential relationships

always In block ,begin--end The code in is assigned a non blocking value <=, Statements are concurrent relationships

initial In block ,begin--end The code in is assigned with blocking =, Statements are sequential relationships , Not recommended for use <= It's easy to get confused

initial In block ,fork--jion The code in is assigned with blocking =, Statements are concurrent relationships

System tasks and functions

$time 、$realtime Is a system function that displays the simulation time scale ,time Show integers ,realtime Display decimal $finish、$stop Is to exit the simulator and end the simulation 、 Pause

$random Generate random numbers . When the function is called, it returns a 32 Random number of bits . This is a signed integer number .

The general usage is :$random%b, among b>0. He gave a range in (-b+1):(b-1) The random number in .

Here's an example :

reg [23:0]rand;

rand=$random%60; // Generate -59~59 Random number between

rand={$random}%60; // Generate 0~59 Random number between

$display(“ Format controller ”, Output variable list ); Call show once , The display ends

$monitor(“ Format controller ”, Output variable list ); Generally, it is placed separately in one initial in , As long as the output variable changes , Then output multiple times

Time units and precision :

`timescale < Time unit > /< Time precision > , Among them, the symbols of time measurement are :s、ms、us、ns、ps and fs

for example :

`timescale 1ns/100ps, It means : The unit of time delay is 1ns, The time accuracy is 100ps( That is, accurate to 0.1ns, After the decimal point 1 Decimal place ).

`timescale 1ns/1ns, It means : The unit of time delay is 1ns, The time accuracy is 1ns( That is, accurate to 1ns, An integer value )

FSM Finite state machine

from Present state logic 、 Substate logic and Output logic form

Moore type : The output is only related to the current state

Rice grain type : The output is related to both the current state and the input

Three paragraph : Present state (CS)、 Substate (NS)、 Output logic (OL) One for each always Process description

Two-stage type :CS+NS,OL Dual process description

One stage : In the single process description , The state of the state machine 、 The substate and output logic are placed in one always Describe in the process

Assembly line

By multiple always Realization , Every always Corresponding to the first stage pipeline

every last always in , The left side of the expression is independently defined by the assigned variable ( Is the intermediate isolation register ), Save the current level of results and unprocessed data . To the right of the expression ( Data sources ), The previous level always From the results in .

always @(posedge clk)

begin tempa=ina; tempb=inb; tempci=cin; end // Input data cache

always @(posedge clk)

begin {firstco,firsts}=tempa[1:0]+tempb[1:0]+tempci; // First stage plus ( low 2 position )

firsta=tempa[7:2]; firstb=tempb[7:2]; end// Data cache not participating in calculation 边栏推荐

猜你喜欢

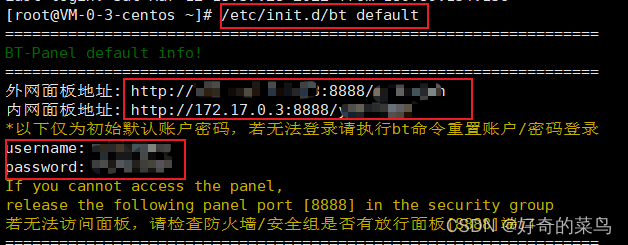

宝塔忘记密码

Badly placed()'s problem

Easy EDA learning notes 09 esp32-wroom-32e module esp32-devkitc-v4 development board one click download circuit

WPF Command指令和INotifyPropertyChanged

How to realize video call and live interaction in a small program when live broadcasting is so popular?

小白投资理财必看:图解基金买入与卖出规则

Endnote20 tutorial sharing (unfinished

![[STL] unordered of associated container_ Map Usage Summary](/img/6a/d614f2f363fa5181c25e79ff8b0dab.png)

[STL] unordered of associated container_ Map Usage Summary

GIS实战应用案例100篇(七十九)-多规整合底图的制作要点

WPF command directive and inotifypropertychanged

随机推荐

312. 戳气球

MySQL index

【STL】顺序容器之deque用法总结

Chrome remove duplicate bookmarks

901. 股票价格跨度

Badly placed ()‘s 问题

Common setup modes (Abstract Factory & responsibility chain mode & observer mode)

mysql 优化

System permission program cannot access SD card

C language operator priority formula

mysql 索引

[STL] summary of map usage of associated containers

322. 零钱兑换

2022年养老理财产品有哪些?风险小的

Run typescript code directly using TS node

Swagger3 integrates oauth2 authentication token

core.js是什么---kalrry

[STL] summary of pair usage

在金融行业做数据产品经理是什么体验

[project training] change of linear arrow