当前位置:网站首页>Axi protocol (1): introduction to AMBA bus, introduction to Axi concept and background, characteristics and functions of Axi protocol

Axi protocol (1): introduction to AMBA bus, introduction to Axi concept and background, characteristics and functions of Axi protocol

2022-07-24 16:44:00 【Dull as dull】

1 AMBA Bus Introduction

AMBA(Advanced Microcontroller Bus Architecture) The bus specification is ARM The bus specification proposed by the company , By most SoC The design adopts , Now let's understand it according to its release version .

- AMBA edition 1 Specification definition :

- ASB(Advanced System Bus)

- APB(Advanced Peripheral Bus);

- AMBA edition 2 Specification definition :

- AHB(Advanced High-performance Bus)

- ASB

- APB

- AMBA edition 3 Specification definition :

- AXI v1.0(Advanced Extensible Interface)

- AHB-Lite v1.0

- APB v1.0

- ATB v1.0(Advanced Trace Bus)

- AMBA edition 4 Specification definition :

- ACE(AXI Coherency Extensions)

- ACE-Lite

- AXI4

- AXI4-Lite

- AXI4-Stream v1.0

- APB v2.0

- ATB v1.1

- The latest generation of AMBA4 The objectives of the specification are as follows :

- Suitable for high bandwidth and low latency design

- Without using complex bridging methods , Allow higher frequency operation

- Meet the requirements of component interface in general

- Suitable for memory controllers with high initial access delay

- Provide flexibility for the implementation of interconnection structure

- Downward compatibility with existing AHB and APB Interface .

A brief introduction to some protocols

AHB For high performance 、 High clock frequency system architecture , With pipeline operation 、 Multiple bus masters 、 Burst transmission 、 Features such as split transactions .

APB Provide a low-power interface , Reduce the complexity of the interface ; For external devices with low bandwidth and no need for high-performance bus ; It belongs to non pipeline structure , All signals are only related to the rising edge of the clock , Latched address and control .

AXI4 The protocol is based on burst transmission mechanism , Have a separate address / Control and data channels ; Use byte gating , Support non aligned data transfer ; Only the burst transaction of the starting address ; Independent read and write data channels ; Enable low-cost direct memory access DMA transmission ; Can send multiple unresolved addresses ; Complete disorderly transactions ; Easy to add register slices , Meet the requirements of timing convergence .

2 AXI Introduction to concept and background

AXI, yes Xilinx from 6 Series of FPGA An interface protocol introduced at the beginning , It mainly describes the data transmission mode between master device and slave device .

AXI yes ARM The company put forward AMBA Part of , It's a high performance 、 High bandwidth 、 Low latency on chip bus , Also used to replace the previous AHB and APB Bus .AXI Technology enriches existing AMBA Standard content , Meet ultra-high performance and complex system on chip (SoC) Design needs .

The first version AXI(AXI3) Included in 2003 Published in AMBA3.0 in

Second version AXI(AXI4) Included in 2010 Published in AMBA4.0 in

Way of understanding , You should drive on the road , Now? AXI It is a standard road , Traffic rules are stipulated, such as driving on the right , How to get off the highway , How to get to other cities .

3 characteristic

- Have a separate address / Control channel and data channel , Information flow is transmitted only in one direction , Simplify the bridge between clock domains , Reduce the number of doors . When the signal passes through a complex system on chip , Reduce delay . Independent address and data channel . Address and data channels are separated , Each channel can be optimized separately , The timing channel can be controlled as needed , Raise the clock frequency to the highest , And minimize the delay .

- Based on burst transmission mechanism (burst) Handle (transaction), And only give a starting address (start-address). Support multiple data exchange . By performing burst operations in parallel , Greatly improve the data throughput , Can complete the task in a shorter time , While meeting the requirements of high performance , Reduced power consumption .

- Will write data (write data channel) And read data channels (read data channel) Separate from , Please note that they are all for data channels , And it can provide a low-power direct memory access (direct memory acess)

- High performance ( High speed , High frequency , High bandwidth , Low latency ) The digital system of

- By means of byte gating (byte strobe), Support non aligned data transmission (unaligned data transfer)

- Support processing multiple unresolved addresses (support for issuing multiple outstanding addresses)

- Support unordered processing (support for out-of-order transaction )

- Provide registers for some timing termination operations .

- It can be matched with a series of components and equipment with complex interfaces , It can provide interconnection for many on-chip structures

- Can be reverse compatible AHB and APB Interface

4 AXI What exactly does the agreement do : Link master and slave devices

In fact, both read and write operations correspond to devices on both sides of the bus link , That is what we often call the main equipment (master) And slave devices (slave).

master/slave Link map .

AXI The protocol mainly defines the following interfaces :

- stay master and interconnect Between

- from slave and interconnect Between devices

- stay master and slave Between

Master equipment and slave equipment refer to AXI Something connected on both sides

边栏推荐

猜你喜欢

剑指 Offer 22. 链表中倒数第k个节点

MySQL basic commands

VSCode如何鼠标滚轮放大界面

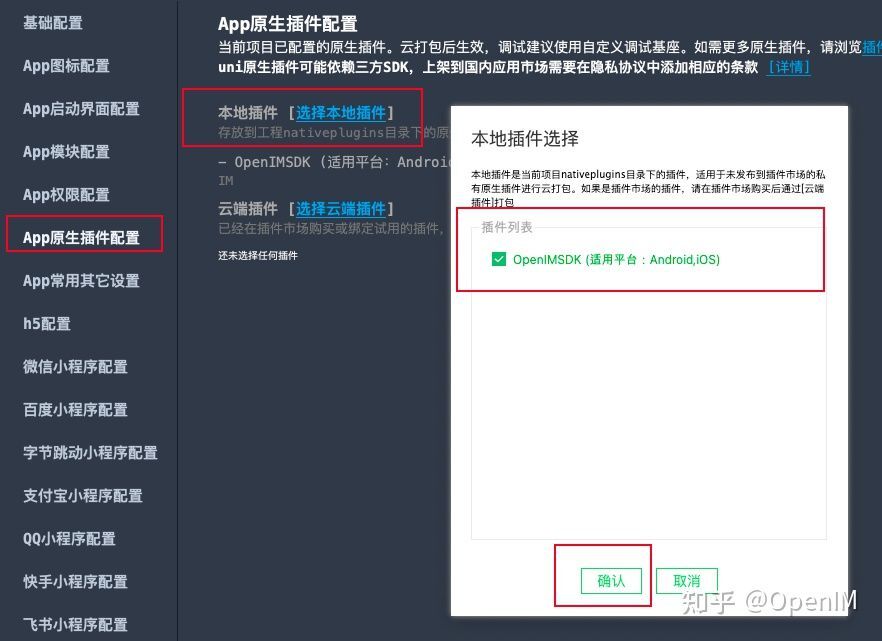

Long awaited full platform support - Open Source im project uniapp update of openim

Problems encountered in upgrading chrome to version 80 - solutions to system login failure

小端格式和大端格式(Little-Endian&Big-Endian)

Win10 download address

PS pull out logo

1184. 公交站间的距离

Mcd12q1 data shows multiple classifications in envi

随机推荐

Development dynamics | stonedb 2022 release milestone

Interview question 01.02. determine whether it is character rearrangement

[LeetCode]38.报数——题解(执行用时击败91% ,内存消耗击败 97%)

ZCMU--5023: 家庭划分(C语言)

QT generation connection Library

JS, call in the for loop is asynchronously converted to synchronous execution

What are the safe securities companies? I want to buy stocks on my mobile phone

Analysis of double pointer sliding window method and solution of leetcode related problems

“天上天下,唯我独尊”——单例模式

AXI协议(3):AXI架构的握手机制和实现细节

文件浏览器?Qt也可以实现!

SS-Paper【1】:Fully Convolutional Networks for Semantic Segmentation

TCP protocol debugging tool tcpengine v1.3.0 tutorial

Jing Wei PS tutorial: basic part a

Dongfang Guangyi refuted the rumor late at night, saying that the news that the hammer was filed for investigation was untrue!

Educational codeforces round 100 (rated for Div. 2) B. find the array solution

会议OA项目进度(二)

Summary of experience in using.Net test framework xUnit, mstest, specflow

Intel plans to sell baseband chip business, but Apple has given up?

图片浏览器?Qt也可以实现!