当前位置:网站首页>SystemVerilog (12) - $unit declaration space

SystemVerilog (12) - $unit declaration space

2022-06-22 18:36:00 【Broken thoughts】

| note |

|---|

| $unit Is a dangerous shared namespace , Full of danger . Its use will make the design difficult to compile and maintain . |

| The following unit representative $unit |

Will be package Add to SystemVerilog Before standard ,SV Provides a different mechanism to create definitions shared by multiple modules . This mechanism is called unit Pseudo global namespace of , Also known as unit Compile unit or declaration space . Any declaration outside the declaration space is in unit In the declaration space . In the following example ,bool_t Is defined outside of two modules , So in unit In the declaration space .

unit A declaration space can contain the same as package User defined of the same type , And have the same comprehensive limitations . However , Unlike the bag ,unit Declaration space can make design code difficult to maintain ,EDA It is also difficult to compile . Use unit Some of the dangers of include

With unit The definition of a declaration space can be scattered across many files , Make code maintenance and code reuse a nightmare , When referencing user-defined types in the package 、 Mission 、 Function or other identifier name , The definition of identifier names is relatively easy to find and maintain . There is always an explicit package reference or package import statement to show where the definition can be found . When in unit User defined types are defined in the declaration space 、 Mission 、 Function or other identifier , This definition can be found in any file that makes up the source code for the design and verification test bench 、 Any directory 、 In any server . location 、 It is difficult to maintain and redefine .

When unit When a definition in a declaration space is in more than one file , These files must be compiled in a specific order .

SystemVerilog Requires that the definition be compiled before it is referenced . When unit When declarations are scattered in many files , Compiling all the files in the right order can be difficult , It's not even possible .

change unit Define all source code files that need to be recompiled .

Yes unit Any changes defined in the declaration space require recompiling all the source code that makes up the design and validation testbed , Because any file anywhere can use this definition without importing . Many software tools do not force recompilation of all files , But if you don't recompile , Design modules may end up using outdated definitions .

For simulation and synthesis ,unit The declaration space can be the same , But it's usually different .

Each call to the compiler starts a new unit Declaration space , This space does not share other unit Declarations in the declaration space . many SystemVerilog The emulator compiles multiple files together . These tools will see a unit Space . In a file unit The definition is visible to any subsequent files in a single compilation . majority SystemVerilog Integrated compilers and some emulators support separate file compilation , Each file can be compiled independently . These tools will see several disconnected unit Declaration space . In a file unit The definition is not visible to any other file .

It's easy to have duplicate identifier names with different definitions .

stay SystemVerilog in , It is illegal to define the same name more than once in the same namespace . If a document is in unit The declaration space defines bool_t User defined types , And the other file is in unit The declaration space also defines bool_t User defined types , Then these two files can never be compiled together , Because these two definitions will eventually be in the same unit End in space . To avoid this conflict , The engineer must use ’define and ’ifdef Add conditional compilation instructions , So that only the first definition encountered by the compiler is compiled .

Packages can be imported into unit in , But its harm is directly related to unit Hazards defined in . Besides , Care must be taken not to import the same package into the same... Multiple times unit Declaration space , It's illegal .

| Best practice guide 4-2 |

|---|

| Avoid like Bubonic plague The use of $unit! contrary , Use packages to share definitions . |

| Package avoided $unit All hazards , Packages provide a controlled declaration space that is easy to maintain and reuse . |

SystemVerilog( Ten )- User defined types

SystemVerilog( 11、 ... and )-SystemVerilog package

边栏推荐

- How can I automatically make an appointment to make a new debt? Is it convenient and safe to make an appointment to make a new bond

- Preliminary controller input of oculus learning notes (1)

- 今天19:30 | 科普大佬说,带大家探寻AI如何激发人类的创造力

- How does flynk MySQL CDC guarantee the server_ Is the ID globally unique?

- 让RDS(for MySQL)数据库的慢日志、审计日志跨空间转存OBS变得更加自动化

- Noah fortune plans to land on the Hong Kong Stock Exchange: the performance fell sharply in the first quarter, and once stepped on the thunder "Chengxing case"

- 【工具】pip和conda的相关使用

- 网络智能运维助力运维效率提升

- 怎么才能自动预约打新债?预约打新债方便安全吗

- 利用Inkscape转换为dxf文件的正确方法 svg导出dxf文件

猜你喜欢

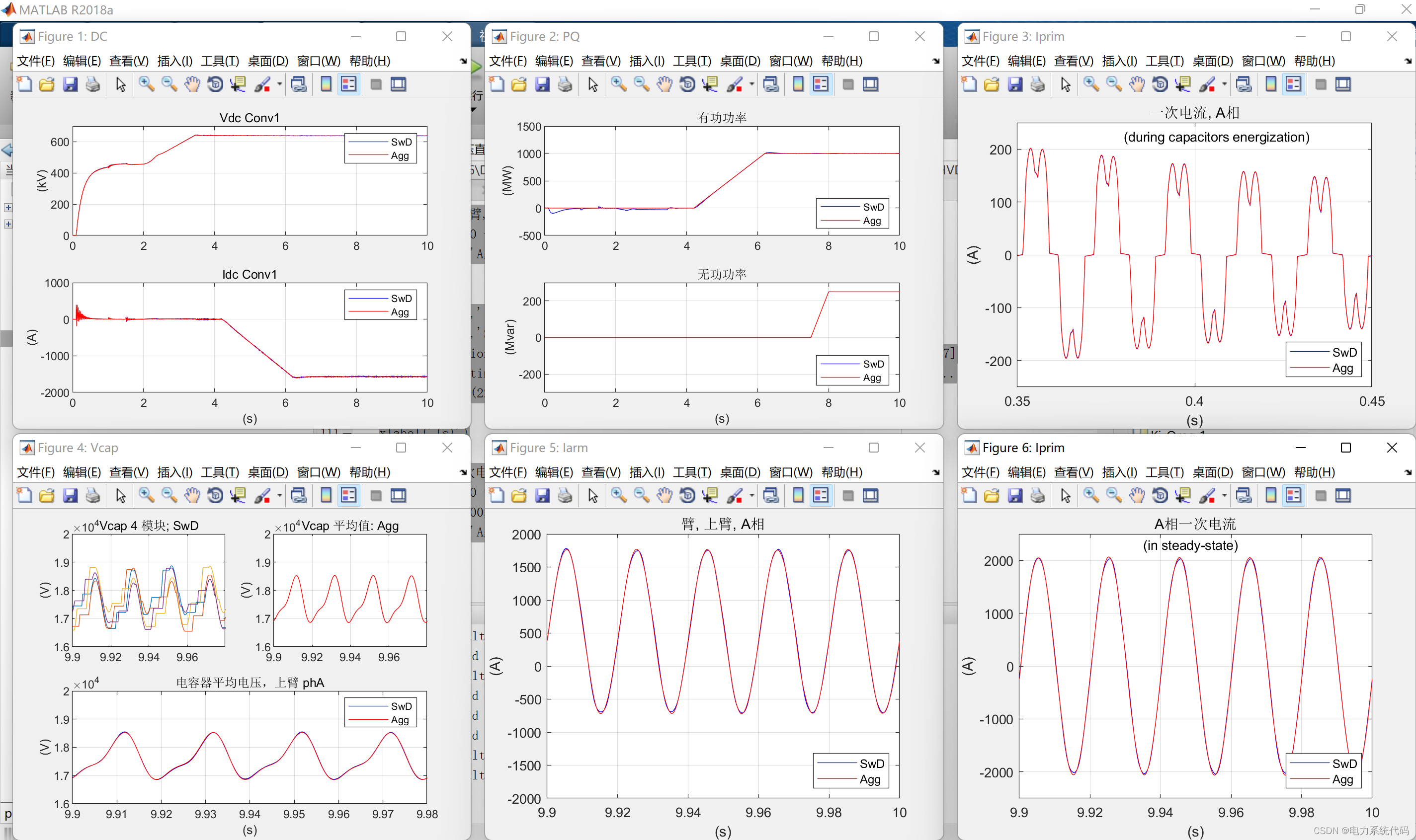

基于转换器 (MMC) 技术和电压源转换器 (VSC) 的高压直流 (HVDC) 模型(Matlab&Simulink实现)

数据库行业分析:从全球IT产业趋势到国产数据库发展之路

Q: how bad can a programmer be?

JSP learning (3) -- JSP implicit object

利用Inkscape转换为dxf文件的正确方法 svg导出dxf文件

Explain the startup process of opengauss multithreading architecture in detail

At 19:30 today, the science popularization leader said that he would take you to explore how AI can stimulate human creativity

Activity启动流程梳理

When do project managers particularly want to escape from work?

项目经理们在哪个时刻特别想逃离工作?

随机推荐

让RDS(for MySQL)数据库的慢日志、审计日志跨空间转存OBS变得更加自动化

Configuration of development environment for JSP learning

Grafana 9 正式发布,更易用,更酷炫了!

Development mode of JSP learning

Nuxt - Universal(SSR / SSG)/ Single Page App(渲染模式)

新手必会的静态站点生成器——Gridsome

怎么才能自动预约打新债?预约打新债方便安全吗

SystemVerilog(十二)-$unit声明空间

请问一下flink mysql-cdc 如何保证server_id全局唯一呢?

Golang实现基于Redis的可靠延迟队列

无心剑中文随感《探求真谛》

Q: how bad can a programmer be?

Some preliminary explorations of avoiding obstacles and finding paths by rays in unity

Live broadcast Preview - 12 first-class Chinese scholars open ICLR 2022

今天19:30 | 科普大佬说,带大家探寻AI如何激发人类的创造力

Conda——基础配置命令总结

RF Analyzer Demo搭建

@Lucky user of "Qilu Duojiao", Shandong 5A scenic spot calls you to visit the park for free!

项目经理们在哪个时刻特别想逃离工作?

【工具】pip和conda的相关使用