当前位置:网站首页>VHDL design

VHDL design

2022-06-26 03:58:00 【@Landscape post yuan】

Libraries and packages (packages)

Declare constants that will be used in the design or entity , data type

Entity (Entities)

Declare interfaces to entities and designs , That is to define the input of this design 、 Out port

Structure (Architectures)

Defines the implementation of entities . That is, the specific description of the circuit

Or gate

LIBRARY IEEE; -- library , Package calls

USE IEEE.STD_LOGIC_1164.ALL

ENTITY MYORY2 IS -- Entity MYORY2 describe

PORT(A,B:IN STD_LOGIC;

C :OUT STD_LOGIC);

END MYORY2;

ARCHITECTURE ART1 OF MYOR2 IS

BEGIN -- Description of structure

C<=A OR B;

END ART1;Half adder

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL

ENTITY H_ADDER IS -- Entity H_ADDER describe

PORT(A,B:IN STD_LOGIC;

CO,SO:OUT STD_LOGIC);

END H_ADDER;

ARCHITECYURE ART2 OF H_ADDER IS -- Description of structure

BEGIN

SO<=(A OR B)AND(A NAND B);

CO<=NOT(A NAND B);

END ART2;Full adder

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITYY F_ADDER IS -- Entity F_ADDER describe

PORT(AIN,BIN,CIN:IN STD_LOGIC;

CY,SUM:OUT:OUT STD_LOGIC);

END F_ADDER;

ARCHITECTURE ART3 OF F_ADDER IS

COMPONENT H_ADDER -- Component call declaration

PORT(A,B:IN STD_LOGIC;

CO,SO:OUT STD_LOGIC);

END COMPONENT;

COMPONENT MYOR2

PORT(A,B:IN STD_LOGIC;

C:OUT STD_LOGIC);

END COMPONENT;

SIGNAL D,E,F:STD_LOGIC; -- Signal declaration

BEGIN

U1:H_ADDER PORT MAY(A=>AIN,B=>BIN

CO=>D,SO=>E);

U2:H_ADDER PORT MAY(A=>E,B=>CIN,

CO=>F,SO=>SUM);

U3:OR2 PORT MAY(A=>D,B=>F,C=>CY);

END ART3;

边栏推荐

- 用eclipse连mysql数据库出错然后出现图中的话是咋回事呀

- 763. 划分字母区间

- 【MySQL】 MySQL 导出数据库

- Can string be changed?

- Comparison of static methods and variables with instance methods and variables

- QPS的概念和实现

- 2020 summary: industrial software development under Internet thinking

- Matplotlib multi line chart, dot scatter chart

- 神经网络学习小记录71——Tensorflow2 使用Google Colab进行深度学习

- Machine learning notes - trend components of time series

猜你喜欢

【LOJ#6718】九个太阳「弱」化版(循环卷积,任意模数NTT)

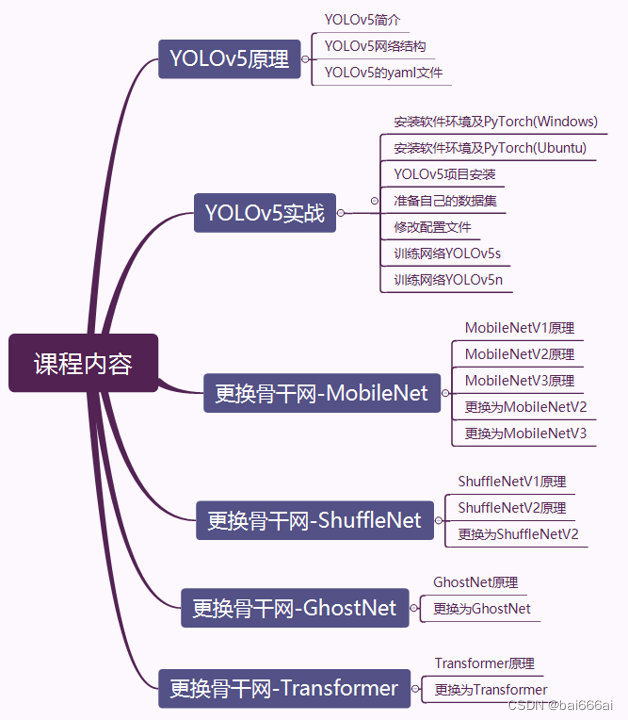

Yolov5 improvements: replace the backbone

User control custom DependencyProperty

matplotlib折线图,文字显示,win10

![[MySQL] MySQL export database](/img/e3/1aa31760dc5447b7c3c0d942644116.jpg)

[MySQL] MySQL export database

Can string be changed?

【QT】对话框dialog

Oracle technology sharing Oracle 19.14 upgrade 19.15

Getting started with flask

Analysis of camera memory memory leakage (II)

随机推荐

After four years of outsourcing, people are directly abandoned...

【QT】对话框dialog

Introduction Guide to the flutterplugin plug-in in the actual combat of flutter

三元损失英文版

阿里云函数计算服务一键搭建Z-Blog个人博客

Uni app, the text implementation expands and retracts the full text

VHDL设计

【Flink】Flink Sort-Shuffle写流程简析

[Flink] Flink source code analysis - creation of jobgraph in batch mode

Getting started with flask

2022.6.25-----leetcode. Sword finger offer 091

軟件調試測試的十大重要基本准則

Matplotlib line chart, text display, win10

Lua语法讲解

(15) Blender source code analysis flash window display menu function

WPF 值转换

mysql 常用语句

Prism framework

Restful API interface design standards and specifications

What preparation should I make before learning SCM?