当前位置:网站首页>Usage of vivado vio IP

Usage of vivado vio IP

2022-06-27 23:23:00 【ML__ LM】

vivado VIO IP Usage of

0 Program function

adopt VIO Analog keys to control DDS The frequency control word , So as to obtain sine waves of different frequencies .

Program structure

Must pass ILA To simulate VIO,testbench Can't simulate VIO.

1 IP Nuclear instantiation

1.1 VIO IP Exemplification of

vio_0 your_instance_name (

.clk(clk), // input wire clk

.probe_out0(probe_out0) // output wire [1 : 0] probe_out0

);

1.2 DDS IP

dds_sin your_instance_name (

.aclk(aclk), // input wire aclk

.s_axis_config_tvalid(s_axis_config_tvalid), // input wire s_axis_config_tvalid

.s_axis_config_tdata(s_axis_config_tdata), // input wire [23 : 0] s_axis_config_tdata

.m_axis_data_tvalid(m_axis_data_tvalid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(m_axis_data_tdata), // output wire [47 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata(m_axis_phase_tdata) // output wire [23 : 0] m_axis_phase_tdata

);

2 Program

2.1 Program structure

2.2 Top level modules

`timescale 1ns / 1ps

module top(

input sys_clk ,// The system clock 50MHz T=20ns

input rst_n // System reset

);

// -----------0、VIO Key control frequency control word (key_PINC)

wire [1:0] key_PINC;

vio_0 vio_0_inst (

.clk(sys_clk), // input wire clk

.probe_out0(key_PINC) // output wire [1 : 0] probe_out0

);

//---------------1、 Signal frequency control module --------------//

wire [23:0] Fword ; // Frequency word

Fword_set Fword_set_inst(

//input

.clk (sys_clk ),

.rst_n (rst_n ),

.key_PINC (key_PINC ),

//output

.Fword (Fword )

);

//---------------2、DDS modular --------------//

//input

wire [0:0] fre_ctrl_word_en ;

//output

wire [0:0] m_axis_data_tvalid ;

wire [47:0] m_axis_data_tdata ;

wire [0:0] m_axis_phase_tvalid ;

wire [23:0] m_axis_phase_tdata ;

assign fre_ctrl_word_en=1'b1;

// Exemplification DDS IP

dds_sin dds_sin_inst (

.aclk (sys_clk ), // input wire aclk

.s_axis_config_tvalid (fre_ctrl_word_en ), // input wire s_axis_config_tvalid

.s_axis_config_tdata (Fword ), // input wire [23: 0] s_axis_config_tdata

.m_axis_data_tvalid (m_axis_data_tvalid ), // output wire m_axis_data_tvalid

.m_axis_data_tdata (m_axis_data_tdata ), // output wire [47 : 0] m_axis_data_tdata

.m_axis_phase_tvalid (m_axis_phase_tvalid ), // output wire m_axis_phase_tvalid

.m_axis_phase_tdata (m_axis_phase_tdata ) // output wire [23 : 0] m_axis_phase_tdata

);

ila_1 ila_1_inst (

.clk(sys_clk), // input wire clk

.probe0(key_PINC), // input wire [1:0] probe0

.probe1(Fword), // input wire [23:0] probe1

.probe2(m_axis_data_tdata) // input wire [47:0] probe2

);

endmodule

2.3 Fword_set modular

`timescale 1ns / 1ps

//

// Press the key to select the corresponding frequency control word , Then select the corresponding signal frequency

//

module Fword_set(

input clk ,

input rst_n ,

input [1:0] key_PINC ,

output reg [23:0] Fword

);

//[email protected](posedge clk or negedge rst_n)

//begin

// if(!rst_n)

// key_sel <= 4'd0;

// else

// key_sel <= key_sel;

//end

// The output frequency(f_out ) , of the DDS waveform is a function of the system clock frequency(f_clk ) .

// the phase width, that is, number of bits (B ) in the phase accumulator

// and the phase increment value (deta_theta) .

// The output frequency in Hertz is defined by:f_out=f_clk*deta_theta/(2^B)

// fre_ctrl_word How to determine ?

// according to IP Nuclear summery, phase width=20bits Frequency per channel=100MHz

// Calculation formula of output frequency f_out=f_clk*deta_theta/(2^B)=100M* 104857/(2^20 )= 10M

[email protected](*)

begin

case(key_PINC)

0: Fword <= 'h28f5; //1Mhz 10485 The value of each phase increase deta_theta

1: Fword <= 'h51eb; //2Mhz 20971

2: Fword <= 'ha3d7; //4Mhz 41943

3: Fword <= 'h19999; //10Mhz 104857

endcase

end

endmodule

2.4 Constraint file

set_property PACKAGE_PIN U18 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN J16 [get_ports rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

# Timing constraints

create_clock -period 20.000 -name sys_clk -waveform {

0.000 10.000} [get_ports sys_clk]

3 result

key_PINC=0(2’b01)

key_PINC=2(2’b10)

边栏推荐

- What problems should be paid attention to in the serpentine wiring of PCB?

- UESTC (shenhengtao team) & JD AI (Mei Tao team) proposed a structured dual stream attention network for video Q & A, with performance SOTA! Better than the method based on dual video representation!

- Arcgis-engine二次开发之空间关系查询与按图形查询

- 小芯片chiplet技术杂谈

- "Top stream Aidou manufacturing machine" cooperates with four industrial capitals to become LP

- Aggregation and index optimization of mongodb basic operations

- 新加坡国立大学|采用无模型强化学习方法评估能源效益数据中心的节能情况

- Spark bug practice (including bug:classcastexception; connectexception; NoClassDefFoundError; runtimeException, etc.)

- Typora 1.2.5等版本下载

- 打造南沙“强芯”,南沙首届IC Nansha大会召开

猜你喜欢

Practice torch FX: pytorch based model optimization quantization artifact

Consumer finance app user insight in the first quarter of 2022 - a total of 44.79 million people

EXCEL 打印设置公共表头

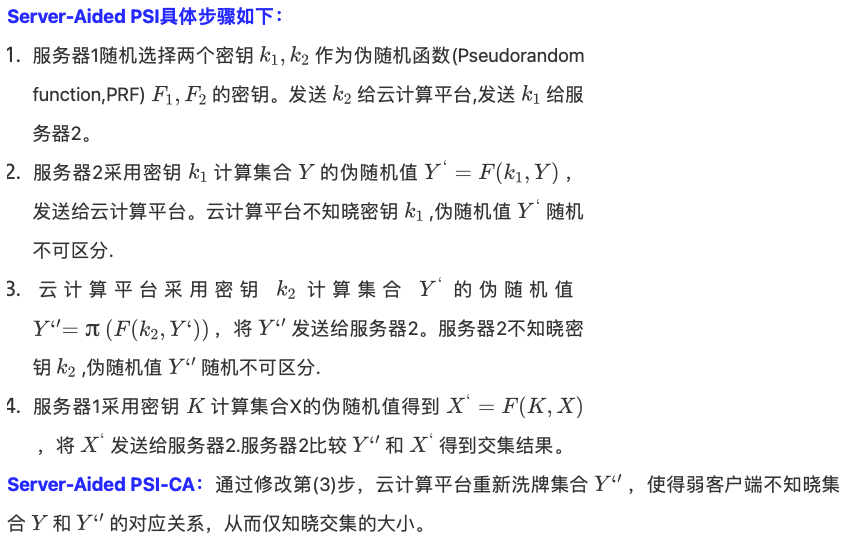

云辅助隐私集合求交(Server-Aided PSI)协议介绍:学习

Livox Lidar+海康Camera实时生成彩色点云

Spark BUG實踐(包含的BUG:ClassCastException;ConnectException;NoClassDefFoundError;RuntimeExceptio等。。。。)

seata

Livox lidar+ Hikvision camera real-time 3D reconstruction based on loam to generate RGB color point cloud

本机部署一个MongoDB单节点服务器,并启用auth验证、开启oplog

广告太「野」,吉野家「渡劫」

随机推荐

Spark bug practice (including bug:classcastexception; connectexception; NoClassDefFoundError; runtimeException, etc.)

Practice torch FX: pytorch based model optimization quantization artifact

Advertising is too "wild", Yoshino "surrenders"

webService

What problems should be paid attention to in the serpentine wiring of PCB?

This kind of people began to be robbed by VC with a monthly salary of 80000 yuan

First principles (optimal solution theory)

Download versions such as typora 1.2.5

小芯片chiplet技术杂谈

本机部署一个MongoDB单节点服务器,并启用auth验证、开启oplog

[网络]常见的请求方法

移动端避免使用100vh[通俗易懂]

Detect objects and transfer images through mqtt

凌云出海记 | 沐融科技&华为云:打造非洲金融SaaS解决方案样板

mongodb基础操作之聚合操作、索引优化

[electron] 基础学习

游戏手机平台简单介绍

Spatial relation query and graph based query in secondary development of ArcGIS Engine

clickonce 部署ClickOnce应用程序时出错-清单中的引用与下载的程序集的标识不匹配

How to start ID from 1 after MySQL deletes a table