当前位置:网站首页>RF_ DC system clock setting gen1/gen2

RF_ DC system clock setting gen1/gen2

2022-06-24 19:59:00 【Hua Weiyun】

RF_DC System clock settings GEN1/GEN2

The system clock configuration interface is shown in the figure , Only in the corresponding Tile ADC/DAC Only when it is enabled can Tile Configure your clock .

In the system PLL block diagram .

It should be noted that at the input end 100R ODT It should be based on mos The structure realizes . Therefore, there is no on-chip matching when the module is not enabled . If there is a clock input at this time, it may cause strong reflection .PG269-page163 Which should be on the enabling chip PLL Add clock later , But in RF_ANAlyzer You need to configure the clock of the board before downloading the bit stream , So the two documents are contradictory . In fact, I have operated in both ways , Also can work normally .

AXI4-Lite Interface Configuration

AXI4 The bus is used for communication in the module ,PG269-Page226 I mentioned AXI4 Clock configuration and DAC ADC Power on sequence of , But there is no specific design rule . Actually demo Set in the for 100

Tile Clock Configuration

- Sampling Rate (GSPS): ADC and DAC Sample rate of actual output

- Max Fs (GSPS): Using chip ADC DAC Maximum sample rate supported

- PLL: Configure whether to use PLL

- Reference Clock (MHz): Tile Actual input clock , This number should be consistent with the value of the previous clock configuration . This value is related to the sampling rate , Because the sampling clock uses this clock to pass through PLL Generated . Please refer to this for specific settings Tile File structure in

- PLL Reference Clock: PLL The input clock of

- Reference Clock Divider: Input clock divider Reference Clock After frequency division, it becomes PLL Reference Clock

- Fabric Clock (MHz): It is difficult to translate this word into Chinese Information 1 Information 2, The original meaning of this word is fabric 、 Cloth 、 structure . The extended meaning here should be closer to the structure , Because from the data 1、2 You can see that this interface is used for PS and PL Links to use . stay RFDC in , This interface is used for AD or DA Data exchange , So the speed of this interface is the same as ADC/DAC The sampling rate of . stay IP The frequency of this interface in the setting is always equal to... Of the sampling rate 1/8. Because of the same Tile There are multiple AD DA So the same tile If the peripheral speed in the is consistent .

- Clock Out (MHz): Tile The output clock of , It can be used to drive DAC Of the input data stream AXI4-Stream Bus . The frequency of this clock is also related to the sampling rate .

PLL Summary Settings

Shows each Tile Of PLL Configuration situation

- Vco(MHz): PLL VCO (voltage controlled oscillator) The output frequency of .8.5-13.2GHz

- Fb Div: Vco Feedback output divider , The range that can be set is 13-160, It can only be an integer

- M: Output frequency division coefficient 2、3、4-64 Even number between

- R: Enter the division factor Only integers can be taken 1-4

PLL Structure

Output frequency formula Fs = (Fin/R)*(FBDiv/M)

- PFD Frequency and phase detector (phase/frequency detector)

- CP Charge pump (charge pump)

- LPF low pass filter (Low Pass Filter)

- VCO VCO (voltage controlled oscillator)

of PLL You can refer to this article for the implementation of The paper

To prevent Links GG, Here I would like to add my own understanding .

The input signal passes through the input frequency divider (Refrence Divider) after , Input to PFD,PFD The essence of can be seen as a comparison output link ,PFD Compare the input signal with the feedback signal . Output a signal related to both frequency and phase ( Ideal ), This signal can be regarded as a square wave signal with variable pulse width . After input to the charge pump, the voltage signal changes into a current pulse , Then it becomes the control voltage of the VCO after the high-frequency component is filtered by the low-pass filter . So far, negative feedback is formed , Until the system stabilizes , PLL lock

边栏推荐

猜你喜欢

To open the registry

LCD12864 (ST7565P) Chinese character display (STM32F103)

Vs2017 add header file path method

Vs2017 setting function Chinese Notes

Network security review office starts network security review on HowNet

![[go Language brossage] go from 0 to Getting started 4: Advanced use of slice, Primary Review and Map Getting started Learning](/img/3a/db240deb4c66b219ef86f40d4c7b7d.png)

[go Language brossage] go from 0 to Getting started 4: Advanced use of slice, Primary Review and Map Getting started Learning

Zadig + 洞态 IAST:让安全溶于持续交付

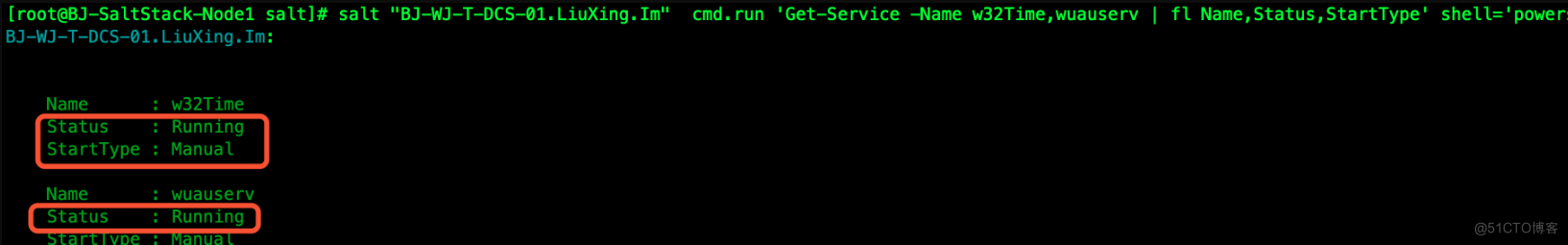

Saltstack state state file configuration instance

What are the functions of IBPs open source form designer?

Methods for comparing float types in the kernel

随机推荐

[R tidyverse] use of select verb

Landcover100, planned land cover website

8 challenges of BSS application cloud native deployment

Volcano成Spark默认batch调度器

华为云ModelArts第四次蝉联中国机器学习公有云服务市场第一!

60 divine vs Code plug-ins!!

Write a positive integer to the node and return a floating-point number multiplied by 0.85 when reading the node

假如,程序员面试的时候说真话

Accurate calculation of task progress bar of lol mobile game

1、 Downloading and installing appium

At present, only CDC monitors Mysql to get the data of new columns. Sqlserver can't, can it

Geoscience remote sensing data collection online

[go Language brossage] go from 0 to Getting started 4: Advanced use of slice, Primary Review and Map Getting started Learning

Oracle create tablespaces and tables

What is CNN (convolutional neural network)

How to use JWT authentication in thinkphp6

thinkphp6中怎么使用jwt认证

Understanding openstack network

Get to know the data structure of redis - hash

If the programmer tells the truth during the interview