当前位置:网站首页>Introduction to armv8 general timer

Introduction to armv8 general timer

2022-07-25 09:56:00 【Work makes me happy】

Preface

Sort out and summarize relevant concepts based on online materials , Part of the content is quoted from the following article .

1 Generic timer One

The content is quoted from the article “Linux One of the time subsystems ( seventeen ):ARM generic timer Driver code analysis ”, Put the link at the end of the text .

1.1 system counter

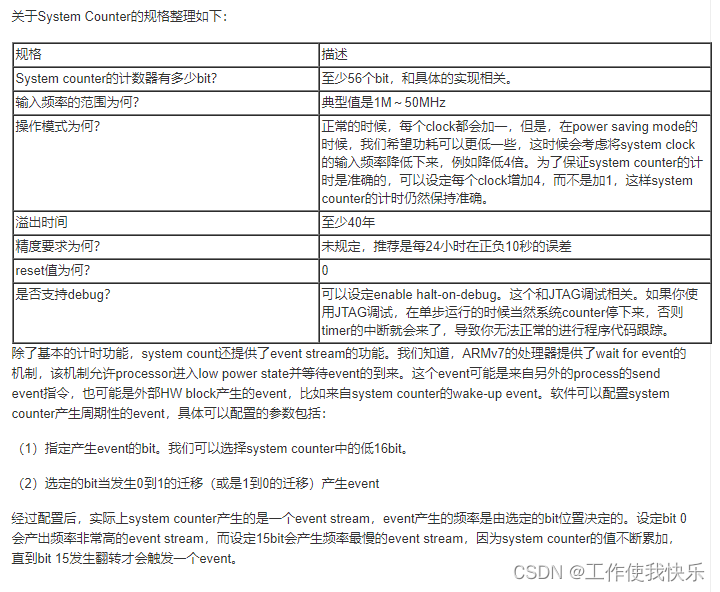

ARM generic timer Related hardware block As shown in the figure below ( Mark it in green ):

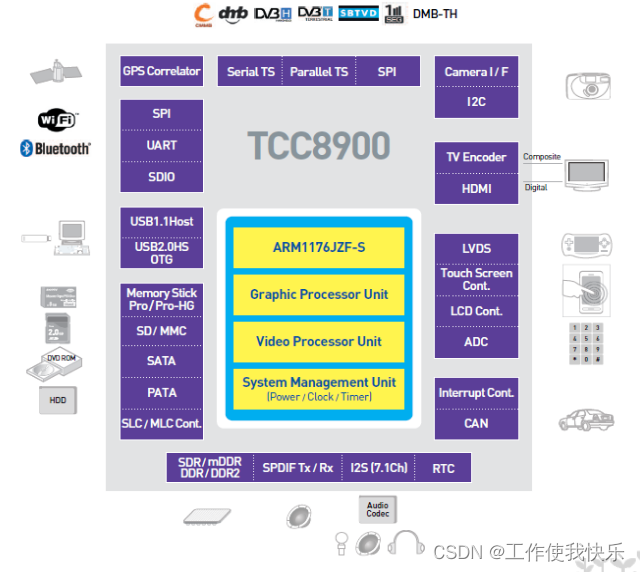

ARM generic timer The hardware block Mainly SOC Upper System counter( Multiple process share , Used to record the passage of time ) And attached to each processor Upper Timer( Used to trigger timer event) form , Other generic timer The hardware circuit of is mainly used for communication generic time event Of . For example, each processor Medium timer and system counter Peripherals interact , each processor Medium timer Information exchange .System counter Its function is very simple , It is to calculate how many input clocks have passed clock, The beginning was 0, every last clock,System counter Will add one .System counter Of counter value It needs to be distributed to all timer in , in other words , From each timer From the perspective of ,system counter value It should be consistent .Timer It's actually a timer , It can define a specified time , When it's time , will assert An external output signal ( It can be output to GIC, As a interrupt source).

from power domain Look at ,ARM generic timer Divided into two parts :System counter And each Multiprocessor In the system Timer_x、 Interface circuit, etc . The reason for this is obvious : Power consumption ( Power management ) Consideration . stay power saving mode Next , Sure shutdown each processor Power supply of the system , But you can keep system counter Power supply of , such , At least the system time can be maintained .

and power domain similar ,clock domain It's also different ,system counter and processor Work in different clock Next , The software has been modified CPU The frequency of will not affect system counter Work rhythm of , It will not change timer act .

1.2 Physical counter

each cpu Of timer It's based on system counter To trigger timer event Of , therefore , There must be a mechanism in the system to make System counter The value of is broadcast to each CPU Of timer HW block On , Run in all at the same time processor The software on can be obtained through the interface System counter Value .

The processor can use CNTPCT Register to get system counter The current value of the , We call it physical counter.

Yes physical There is virtual,processor Can pass CNTVCT Register access virtual counter, however , For not supporting security extension and virtualization extension The system of ,virtual counter and physical counter It's the same value .

1.3 Timers

Every... In the system processor Will attach multiple timer, As follows :

(1) For not supporting security extension Of SOC( I won't support it security extension That means I won't support it virtualization extension),timer There are actually two , One is physical timer, The other is virtual timer. Although there are two , But in terms of behavior ,virtual timer and physical timer Act in concert

(2) For support security extension But does not support virtualization extension Of SOC, Every cpu There are three timer:Non-secure physical timer,Secure physical timer and virtual timer

(3) For support virtualization extension Of SOC, Every cpu There are four timer:Non-secure PL1 physical timer,Secure PL1 physical timer,Non-secure PL2 physical timer and virtual timer

Every timer There will be three registers ( We use it physical timer As an example ):

(1)64-bit CompareValue register. This register matches system counter You can implement a 64 bit unsigned upcounter. If physical counter - CompareValue >= 0 Words , Trigger interrupt . in other words ,CompareValue register It's really just a 64 Bit upcounter, Set to a higher value than the current system counter Larger value , With system counter The continuous accumulation , When system counter value touch CompareValue register When setting the value , You're going to GIC Trigger interrupt .

(2)32-bit TimerValue register. This register matches system counter You can implement a 32 bit signed downcounter( sometimes , Use downcounter It will make software logic easier , see ARM generic timer How thoughtful the designers are ). At the beginning , We can set TimerValue The value of the register is 1000( Suppose we want to down count 1000, Then trigger the interrupt ), Write to this register 1000 In fact, it is set CompareValue register The value of is system counter Value plus 1000. With system counter The value of is accumulating ,TimerValue register The value of is decreasing , On duty <=0 When , You're going to GIC Trigger interrupt

(3)32-bit Control register . This register is mainly for timer Control , Specific include :enable or disable The timer,mask perhaps unmask The timer Of output signal(timer interrupt)

each processor Each of them Timer Can generate interrupts , So it and GIC Interface with . Of course , because timer The interrupt of belongs to each CPU Of , Therefore use PPI Type of interrupt , For details, please refer to GIC file . Of course , If you allow timer Trigger interrupt , Of course, make sure that timer yes enable And is umask Of .

2 Generic timer

Quote article “ARMV8 datasheet Learning notes 4:AArch64 System level architecture Generic timer”, Put the link at the end of the text .

2.1 summary

2.2 complete generic timer Components

2.3 System Counter

2.4 AArch64 generic timer

2.4.1 Physical counter( contain system connter Of count value )

2.4.2 Multiple timers

Reference resources

边栏推荐

- 【RNN】剖析RNN 之 从RNN-(Simple|LSTM) 到 序列生成 再到 seq2seq框架(encoder-decoder,或称为seq2seq)

- MLX90640 红外热成像仪测温模块开发笔记(四)

- 工程仪器振弦传感器无线采集仪的采集数据发送方式及在线监测系统

- Segmentation-based deep-learning approach for surface-defectdetection(基于分割的表面缺陷深度学习检测方法)

- CDA Level1复盘总结

- Swift creates weather app

- LoRA转4G及网关中继器工作原理

- Solve the Chinese garbled code error of qtcreator compiling with vs

- First knowledge of opencv4.x --- image histogram matching

- C语言基础

猜你喜欢

TensorFlow raw_rnn - 实现seq2seq模式中将上一时刻的输出作为下一时刻的输入

CCF 201604-2 俄罗斯方块

Swift creates weather app

Mlx90640 infrared thermal imager temperature measurement module development notes (4)

用ESP32+TM1638实验NTP网络校时闹钟的ARDUINO代码

预测2021年:加速实现RPA以外的超自动化成果

Data viewing and parameter modification of multi-channel vibrating wire, temperature and analog sensing signal acquisition instrument

深入理解pytorch分布式并行处理工具DDP——从工程实战中的bug说起

CCF 201512-4 送货

数字IC设计SOC入门进阶

随机推荐

ADC introduction

Get to know opencv4.x for the first time --- add salt and pepper noise to the image

Development history of convolutional neural network (part)

I2C也可总线取电!

OC -- packaging class and processing object

Get to know opencv4.x for the first time --- add Gaussian noise to the image

Swift creates weather app

基于PackNet的演进——丰田研究院(TRI)深度估计文章盘点(下)

【Tensorflow2安装】Tensorflow2.3-CPU安装避坑指南!!!

MLOps专栏介绍

ADC introduction

MLX90640 红外热成像仪测温模块开发笔记(一)

First knowledge of opencv4.x --- image histogram matching

Solve the Chinese garbled code error of qtcreator compiling with vs

AI模型风险评估 第1部分:动机

[data mining] nearest neighbor and Bayesian classifier

File -- first acquaintance

Terminal definition and wiring of bsp3 power monitor (power monitor)

Fundamentals of C language

深度估计自监督模型monodepth2在自己数据集的实战——单卡/多卡训练、推理、Onnx转换和量化指标评估