当前位置:网站首页>Don't mess with full_ Case and parallel_ CASE

Don't mess with full_ Case and parallel_ CASE

2022-06-26 13:03:00 【Lonely single blade】

List of articles

1.2、 Don't use default sentence

1.3、 Use comprehensive properties FULL_CASE

1.4、 Inconsistent circuit simulation before and after synthesis

Write it at the front

case It can be said that we are FPGA A statement that is frequently used in development . meanwhile ,Verilog Statements are also provided casex and casez For our use . In the use of case At the time of statement , Various synthesis tools provide the following two similar synthesis sentences for us to use ( With Xilinx For example ):FULL_CASE and PARALLEL_CASE

These two comprehensive attributes can help us reduce resources to a certain extent , But its use is also relatively easy to introduce BUG-- The front and back simulations do not match . Next, let's have a look at the pros and cons of this double-edged sword .

1、FULL_CASE Usage of

stay case In the use of statements , We usually add default Statement to explain the output assignment of unused state , If not default Statement usually generates a latch LATCH.

1.1、 Use default sentence

As follows 8 Bit independent hot code encoder , We use it default The statement instructs all divisions 8 Other states of a useful state .8 position 2 Hexadecimal numbers can collectively represent 256 Status , This is the only one 8 The first state is the only hot code , The rest is what we don't need . Use default The output of the statement is all connected to a unified 0. however , Although we don't need to use other states , But the integrated circuit will also have coding parts of other states .

module one_hot(

input [7:0] sel,

output reg [2:0] out

);

always @(*) begin

case(sel)

8'b0000_0001 : out = 3'b000;

8'b0000_0010 : out = 3'b001;

8'b0000_0100 : out = 3'b010;

8'b0000_1000 : out = 3'b011;

8'b0001_0000 : out = 3'b100;

8'b0010_0000 : out = 3'b101;

8'b0100_0000 : out = 3'b110;

8'b1000_0000 : out = 3'b111;

default : out = 3'b001;

endcase

end

endmoduleThe following figure shows the integrated circuit structure , Is a pure combinational logic coding circuit .

Resources used :6 individual LUT.

1.2、 Don't use default sentence

Next, put default Comment out the statement , Thus, in the case of non unique hot code state , The output can only remain unchanged , in other words 3bit Output should output 3 A latch LATCH.

The integrated circuit structure is as follows , As expected , Combinatorial logic LUT+ Latch LATCH.

Resources used :5 individual LUT + 3 individual FF(FF Transformative LATCH).

1.3、 Use comprehensive properties FULL_CASE

So the comprehensive properties FULL_CASE What are the ?

FULL_CASE The function of is to tell the comprehensive tool , In this case In the sentence , I've listed all the necessary information , The rest is what I don't need , You can't generate any more superfluous circuits .

Or the example above ,8bit Single hot code coder , I have already put 8 All the hot codes are listed , The rest 256-8=248 All the stinky fish and rotten shrimp are not in the form of a single hot code , I'm sure I won't use , So I warn you ( Integrated tools ) Better be sensible , Do not generate the coding circuit corresponding to the remaining coding .

module one_hot(

input [7:0] sel,

output reg [2:0] out

);

always @(*) begin

(* full_case *)case(sel) // All the necessary conditions are listed

8'b0000_0001 : out = 3'b000;

8'b0000_0010 : out = 3'b001;

8'b0000_0100 : out = 3'b010;

8'b0000_1000 : out = 3'b011;

8'b0001_0000 : out = 3'b100;

8'b0010_0000 : out = 3'b101;

8'b0100_0000 : out = 3'b110;

8'b1000_0000 : out = 3'b111;

//default : out = 3'b001;

endcase

end

endmoduleIntegrated circuit , It uses a lot less resources than the above two cases . Because the extra 248 Status vivado No need to code , Only need to 8 Only one hot code state can be encoded .

Resources used :3 individual LUT.

1.4、 Inconsistent circuit simulation before and after synthesis

The advantages are obvious , Is to save resources . The disadvantages are also obvious , That's it FULL_CASE Statement is a comprehensive attribute , Only in vivado Yes RTL To synthesize ,translate Only when it is used as a circuit , It is not applicable to functional simulation , That is to say, it will cause inconsistency between the simulation results before and after , Easy to introduce BUG.

We can write a simple testbench Before the comprehensive 、 The integrated function simulation is tested .

`timescale 1 ns/ 1 ns

module one_hot_tb();

reg [7:0] sel;

wire [2:0] out;

one_hot one_hot_inst(

.sel (sel),

.out (out)

);

initial begin

sel=8'b0;

# 400 $finish; //200ns End simulation after

end

always #10 sel = {$random}%256; // no 10ns Generate a 0~255 The random number

endmoduleThe functional simulation results before synthesis are as follows :

Because before sel Values are not unique hot code values , So the output out Cannot be encoded , No use default sentence , So the output at this time is x. Until the first single hot code 00000001 appear , Output starts encoding to 000. And then it doesn't conform to the rule of single hot code , Unable to encode , So the output value remains the same as the previous value , Becomes a de facto latch .

Until the input becomes 10000000 and 00100000 after , The output starts to become the corresponding encoded value .

The functional simulation results after synthesis are as follows :

As a result, no latch is generated , Even for non exclusive hot codes , There is also a default encoding value .

1.5、 trap

In general ,FULL_CASE Statements are not recommended , Unless you treat your own RTL Deep understanding of code and circuit structure . Here are some pitfalls for using this statement .

( Situation 1 : There may also be latches )

There is a saying that :FULL_CASE Statement skills reduce resource use , It also eliminates latches . But it is not , In some cases FULL_CASE Statements do not eliminate latches , such as :

module addrDecode1a (mce0_n, mce1_n, rce_n, addr);

output mce0_n, mce1_n, rce_n;

input [31:30] addr;

reg mce0_n, mce1_n, rce_n;

always @(addr)

(* full_case *)casez (addr)

2'b10: {mce1_n, mce0_n} = 2'b10;

2'b11: {mce1_n, mce0_n} = 2'b01;

2'b0?: rce_n = 1'b0;

endcase

endmoduleIntegrated circuit structure : It can be seen that it is still integrated 2 A latch . This is because in the case In the execution statement , At the same time, multiple variables and single variables are assigned , This makes it impossible for some variables to perform output under certain conditions .

The solution to this situation , Is in the case Statement to assign values to all variables , The latter is used directly default sentence , Let all situations have an entrance .

( Situation two : Unexpected circuit structure )

Sometimes , If you don't pay attention to the structure of the circuit , Must use FULL_CASE In words , It will even synthesize circuits that are completely different from the expected functions . such as :

// no full_case

module code4a (y, a, en);

output [3:0] y;

input [1:0] a;

input en;

reg [3:0] y;

always @(a or en) begin

y = 4'b0; // The initial assignment , Prevent latches in other cases where there is no entry

case ({en,a})

3'b1_00: y[a] = 1'b1;

3'b1_01: y[a] = 1'b1;

3'b1_10: y[a] = 1'b1;

3'b1_11: y[a] = 1'b1;

endcase

end

endmoduleIn the example above , First, through y = 4'b0; An entry for assignment is provided for all cases , Prevents the generation of latches . then en As an enable signal , Only if its high level is active , To select the address signal a Corresponding output y[a] The value of is raised .

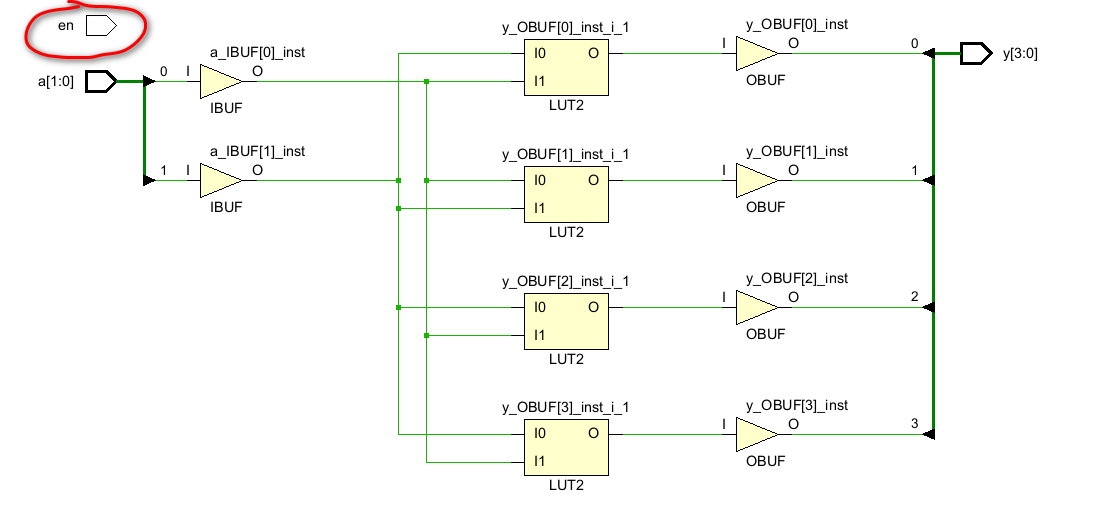

The integrated circuit is as follows : You can see everyone y The output of all has en Participate in operation .

Because the address selection signal only has 2 position , So the biggest one is 4 In this case , In the above code , These four cases are just listed . therefore , You think you can use it at this time FULL_CASE Statement , Maybe it can save some circuit area . therefore , Let's see what happens next .

This is used FULL_CASE A circuit synthesized after a statement :

Look for the , The most outrageous thing about this circuit is , Enable signal en It has nothing to do with the whole circuit . Why is that ?

This is because , Although when the enable signal is set , Address selection signal a Only 4 Status ; But when the enable signal is invalid , Address selection signal a There are also 4 Status . If used FULL_CASE sentence , The synthesis tool may think that the address selection signal a All the cases have been listed , that case Statement {en,a} Just start with one 3bit The signal becomes 2bit The signal , And automatically turn the enable signal en It's ignored !

2、PARALLEL_CASE Usage of

Learning comprehensive sentences PARALLEL_CASE You may need to review before using casex and casez Use of statements .Verilog in case,casez,casex Usage of sentences

Sometimes I use case When the sentence is , The resulting circuit will have priority . If you want no priority , That is, all inputs are parallel , What to do ? The answer is to use comprehensive attributes PARALLEL_CASE.

PARALLEL_CASE The function of is to tell the comprehensive tool , In this case In the sentence , All the cases I have listed are parallel , No priority is required , Don't generate circuits for me by priority !

For example, use casez Examples of statements , If not used PARALLEL_CASE attribute , The integrated circuit must have priority :

module intctl2a (int2, int1, int0, irq);

output int2, int1, int0;

input [2:0] irq;

reg int2, int1, int0;

always @(irq) begin

{int2, int1, int0} = 3'b0;

casez (irq)

3'b1??: int2 = 1'b1;

3'b01?: int1 = 1'b1;

3'b001: int0 = 1'b1;

endcase

end

endmoduleThe integrated circuit is as follows . You can see int2 Only by irq[2] decision ,int1 from irq[2] and irq[1] decision ,int0 By irq[2], irq[1] and irq[0] decision . This is because case Statement is yes priority Of , The priority written in front is the highest .

Next, we add the comprehensive attribute statement :(* parallel_case *).

module intctl2a (int2, int1, int0, irq);

output int2, int1, int0;

input [2:0] irq;

reg int2, int1, int0;

always @(irq) begin

{int2, int1, int0} = 3'b0;

(* parallel_case *)casez (irq)

3'b1??: int2 = 1'b1;

3'b01?: int1 = 1'b1;

3'b001: int0 = 1'b1;

endcase

end

endmoduleThe integrated circuit is as follows . The modified circuit has no priority , They all correspond to bit Of irq The signal directly controls the corresponding int The signal .

parallel_case And full_case The comprehensive properties are the same , One of the biggest problems is the inconsistency of simulation results before and after synthesis , Easy to introduce BUG.

3、 summary

- casez Statements should be used with caution , and casex Statement, try not to use

- If the plan Verilog Add in code “full_case parallel_case” Instructions , You need more understanding of the design RTL Have a comprehensive and in-depth understanding

- Don't abuse only full_case and parallel_case, In general, it is only used to optimize the state machine design of single hot code

- The most important point , Compared with the use of “full_case” and “parallel_case” Instructions , A better approach is to write complete and parallel case sentence !

.

边栏推荐

- NoSQL mongodb - 01 introduction to NoSQL and mongodb

- Redis learning - 04 persistence

- Detailed explanation of C const: definition and use of C constant

- [geek challenge 2019] rce me 1

- First knowledge - Software Testing

- processing 函数translate(mouseX, mouseY)学习

- Processsing 鼠标交互 学习

- processing 随机生成线动画

- solo 博客系统的 rss 渲染失败

- 小白懒人专用-win10-win11一键安装版

猜你喜欢

.NET MAUI 性能提升

记一次phpcms9.6.3漏洞利用getshell到内网域控

倍福将EtherCAT模块分到多个同步单元运行--Sync Units的使用

国标GB28181协议EasyGBS级联宇视平台,保活消息出现403该如何处理?

黑马笔记---常用API

四类线性相位 FIR滤波器设计 —— MATLAB源码全集

由错误<note: candidate expects 1 argument, 0 provided>引发的思考

Deeply analyze the differences between dangbei box B3, Tencent Aurora 5S and Xiaomi box 4S

倍福CX5130换卡对已有的授权文件转移操作

Less than 40 lines of code to create a blocprovider

随机推荐

KVM video card transparent transmission -- the road of building a dream

第01章_Linux下MySQL的安装与使用

Stream learning record

计组实践实验9——使用CMStudio设计基于分段模型机微程序指令(2)

Echart堆叠柱状图:色块之间添加白色间距效果设置

几行代码就能实现复杂的 Excel 导入导出,这个工具类真心强大!

软件测试报告应该包含的内容?面试必问

使用SSH密钥对登陆服务器

MySQL 自定义函数时:This function has none of DETERMINISTIC, NO SQL 解决方案

[esp32-C3][RT-THREAD] 基于ESP32C3运行RT-THREAD bsp最小系统

软件测试 - 概念篇

LeetCode_栈_中等_150. 逆波兰表达式求值

Websocket and socket IO case practice

倍福EtherCAT Xml描述文件更新和下载

小白懒人专用-win10-win11一键安装版

P5733 [deep foundation 6. example 1] automatic correction

C# 结构体:定义、示例

.NET MAUI 性能提升

复制多个excel然后命名不同的名字

NoSQL mongodb - 01 introduction to NoSQL and mongodb