当前位置:网站首页>Vivado error code [drc pdcn-2721] resolution

Vivado error code [drc pdcn-2721] resolution

2022-06-26 13:06:00 【On the way】

Not just solve error , More records and summaries . come on. !

Catalog

explain

VIVADO IDE :2021.1

operating system :WIN 10

FPGA Chip family :Kintex 7 (xc7k410tffg900-2L)

Problem description

Recently, I was debugging a signal processing board , Onboard chip is XILINX Of 7 series FPGA(xc7k410tffg900-2L).MGT BANK The reference clock for is 156.25MHz The differential clock , By CDCM6208 Output driver of clock chip .CDCM6208 When the configuration is complete , The first task is to verify the 156.26MHz Does the differential clock really enter FPGA Of MGT BANK. The specific verification steps are as follows :

First step : Use The original language IBUFDS_GTE2 take MGT BANK The differential reference clock of is introduced and converted to Single ended clock of the same frequency .

Instantiate in the code :

IBUFDS_GTE2 #(

.CLKCM_CFG("TRUE"), // Refer to Transceiver User Guide

.CLKRCV_TRST("TRUE"), // Refer to Transceiver User Guide

.CLKSWING_CFG(2'b11) // Refer to Transceiver User Guide

)

IBUFDS_GTE2_inst (

.O(O_CLK_156M25), // Output 156.25M Single ended clock

.ODIV2(), // The port can be idle

.CEB(1'b0), // The low level input of this port is valid Always give 0

.I (I_CLK_156M25_P), // BANK Reference clock Input port P

.IB(I_CLK_156M25_N) // BANK Reference clock Input port N

);The second step : Send the single ended clock output by the primitive into MMCM perhaps PLL Frequency division , For system design

That's probably the problem , If you don't go in MMCM perhaps PLL, There may be no errors

clk_wiz_1 instance_name1

(

// Clock out ports

.clk_out1(CLK_10M), // output clk_out1

// Status and control signals

.reset(0), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(O_CLK_156M25)); // input clk_in1Then in the process of implementation, it will report DRC Error of , Against the design rules (Design Rule):

[DRC PDCN-2721] IBUFDS_GT_loads_clock_region: IBUFDS_GTE2 IBUFDS_GTE2_inst drives MMCME2_ADV instance_name1/inst/mmcm_adv_inst in a different clock region and must do so using local routing resources which may negatively affect clock performance. Use CLOCK_DEDICATED_ROUTE set to FALSE to indicate this is intended.

The general reason for the mistake is IBUFDS_GTE2 Primitive out of the clock area and driven by MMCM or PLL The clock area of is inconsistent . Be careful , Personally, I think the concept of clock area here is the area of clock resource distribution on the physical level , Different from STA( Static time series analysis ) The concept of clock domain .

Solve mistakes

In fact, the solution has been given at the end of the error . Need to be in XDC The following constraints are made in the document :

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets O_CLK_156M25]Then the bit stream can be generated without error ~

The above is right and wrong [DRC PDCN-2721] The record of , Welcome to leave a message , Add ~

Refer to the official website for solutions : Official forum

边栏推荐

- Sharing ideas for a quick switch to an underlying implementation

- 10秒内完成火灾预警,百度智能云助力昆明官渡打造智慧城市新标杆

- H - Sumsets POJ 2229

- 倍福PLC基于CX5130实现数据的断电保持

- E - Apple Catching

- 自定义封装下拉组件

- 别乱用 FULL_CASE 和 PARALLEL_CASE

- Copy multiple Excel files and name them different

- Digital signal processing -- Design of linear phase type (Ⅰ, Ⅲ) FIR filter (1)

- Angle de calcul POSTGIS

猜你喜欢

What are the common categories of software testing?

倍福PLC选型--如何看电机是多圈绝对值还是单圈绝对值编码器

软件测试测试常见分类有哪些?

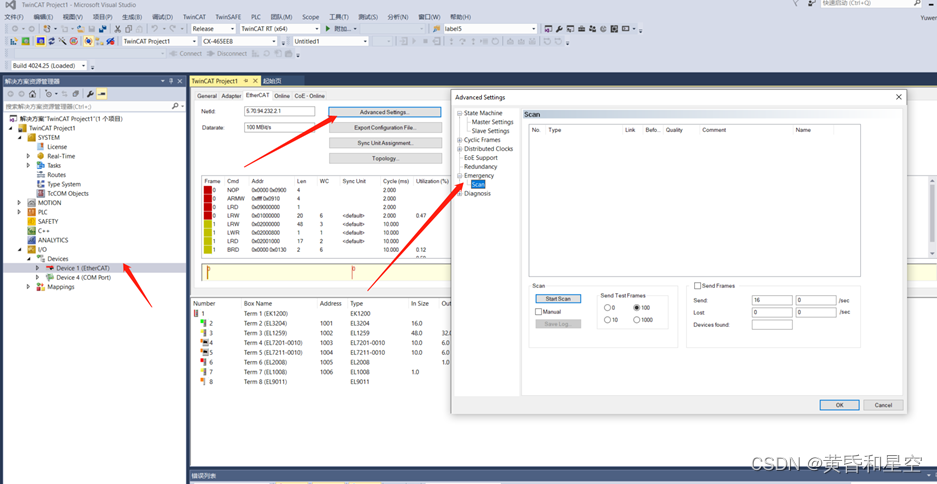

倍福TwinCAT通过Emergency Scan快速检测物理连接和EtherCAT网络

Openlayers drawing dynamic migration lines and curves

Unit practice experiment 8 - using cmstudio to design microprogram instructions based on basic model machine (1)

【网络是怎么连接的】第一章:浏览器生成消息

倍福将EtherCAT模块分到多个同步单元运行--Sync Units的使用

![Vivado 错误代码 [DRC PDCN-2721] 解决](/img/de/ce1a72f072254ae227fdcb307641a2.png)

Vivado 错误代码 [DRC PDCN-2721] 解决

详细讲解C语言10(C语言系列)

随机推荐

P2393 yyy loves Maths II

倍福TwinCAT通过Emergency Scan快速检测物理连接和EtherCAT网络

国标GB28181协议EasyGBS级联宇视平台,保活消息出现403该如何处理?

IDC报告:百度智能云AI Cloud市场份额连续六次第一

Electron official docs series: Testing And Debugging

map 取值

【网络是怎么连接的】第二章(下):一个网络包的接收

POJ 3070 Fibonacci

zoopeeper设置acl权限控制(只允许特定ip访问,加强安全)

Electron official docs series: Processes in Electron

Go structure method

HDU 3709 Balanced Number

倍福PLC旋切基本原理和应用例程

中国剩余定理模板题 互质与非互质

Learning Processing Zoog

Goto statement to realize shutdown applet

倍福通过CTU和TON实现时间片大小和数量的控制

Do you know the limitations of automated testing?

倍福EtherCAT Xml描述文件更新和下载

国标GB28181协议EasyGBS视频平台TCP主动模式拉流异常情况修复