当前位置:网站首页>Introduction to stm32

Introduction to stm32

2022-06-27 02:09:00 【Xiao Hou_ two thousand and twenty-two】

Introduction

1. What's in the chip

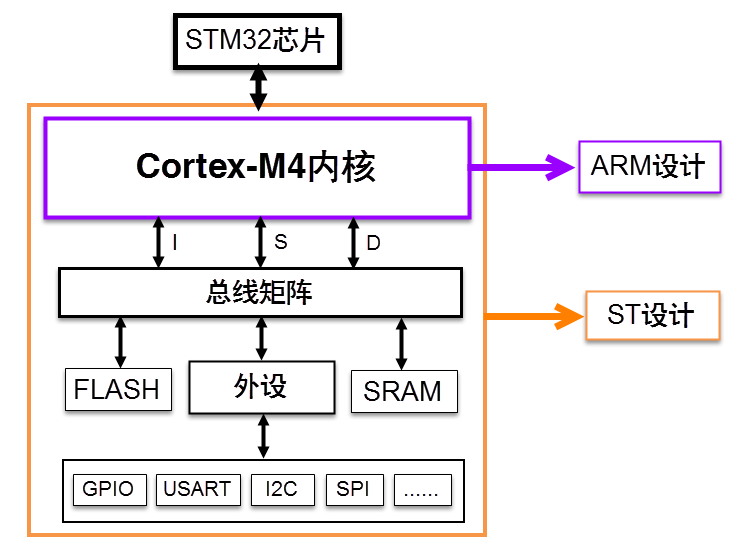

What we see STM32 Chips are packaged products , Mainly by Kernel and on-chip peripherals form .

Pictured here STM32 Schematic of the chip architecture

chip ( This is the kernel , Or call it CPU) And peripherals through a variety of bus connection , The driving unit has 4 individual , Passive units also have 4 individual , See Fig STM32F1Oxx System diagram . For ease of understanding , We can all understand the driver unit as CPU part , Passive units are understood as peripherals . Next, let's briefly introduce the components of the driving unit and the passive unit .

1.1 ICode Bus

ICode Medium I Express Instruction, Immediate instruction . The programs we have written are all instructions after compilation , Store in FLASH in , If the kernel wants to read these instructions to execute the program, it must pass ICode Bus , It needs to be used almost all the time , It's used to take fingers .

1.2 Drive unit

1.2.1 DCode Bus

DCode Medium D Express Data, Data , That means This bus is used for data retrieval . When we write the program , The data are Constant and Variable Two kinds of , Constant is fixed , use C In language const Keyword modification , It's inside FLASH In the middle of , Variables are variable , Both global variables and local variables are placed inside SRAM. Because data can be Dcode Bus and DMA Bus access , So to avoid access conflicts , When fetching data, it needs to go through a bus matrix to arbitrate , Decide which bus is fetching data .

1.2.2 The system bus (system)

System bus is mainly used to access registers of peripheral devices , We usually call it register programming , That is, reading and writing registers are completed through this system bus .

1.2.3DMA Bus

DMA Bus also It is mainly used to transmit data , This data can be in the data register of a peripheral device , Can be in SRAM, It can be inside FLASH. Because data can be Dcode Bus and DMA Bus access , So to avoid access conflicts , When fetching data, it needs to go through a bus matrix to arbitrate , Decide which bus is fetching data .

1.3 Passive unit

1.3.1 Internal flash memory (FLASH)

The internal flash memory is FLASH, This is where we put our programs . The kernel passes through ICode Bus to get the instructions inside .

1.3.2 Inside SRAM

Inside SRAM, That is what we usually say RAM, Program variables , The overhead of stacks and so on is internal SRAM. The kernel passes through DCode Bus to access it .

1.3.3 FSMC

FSMC Our English full name is Flexible static memory controller, It's called flexible static memory controller , yes STM32F1Oxx One of the most distinctive peripherals in , adopt FSMC, We can expand memory , Such as the external SRAM,NAND-FLASH and NORFLASH. But one thing we should pay attention to is ,FSMC Only static memory can be expanded , In the name of S:static, It can't be dynamic memory , such as SDRAM You can't expand .

1.3.4 AHB To APB The bridge of

from AHB Bus Two extended lines APB2 and APB1 Bus , It's loaded with STM32 Various characteristic peripherals . What we often say GPIO、 A serial port 、I2C、SPI These peripherals are mounted on these two buses , This is what we learn STM32 Key points of , Is to learn how to program these peripherals to drive a variety of external devices .

2. Memory mapping

In the figure STM32 F10xx In the system block diagram ,* The controlled unit is FLASH,RAM,FSMC and AHB To APB The bridge of ( Peripherals on chip ), These functions are arranged together in a 4GB In the address space of .* When we're programming , You can find them by their address , Then operate them ( adopt C Language reads and writes data to them ).

** The memory itself has no address information ,** Its address is assigned by the chip manufacturer or user , The process of assigning addresses to memory is called memory mapping , See memory mapping for details . If you assign another address to memory, it is called memory remapping .

2.1 Memory area function division

Here 4GB In the address space of ,**ARM It has been divided into the average of thick lines 8 Block , each 512MB,** Each block also defines its purpose , See table memory function classification for specific classification . The size of each block has 512MB, Obviously it's very big , Chip manufacturers may not always use up when designing their own peripherals within the scope of each block , It's just part of it .

2.2 STM32 Peripheral address mapping for

On chip peripherals are divided into three buses , Depending on the speed of the peripheral , Different buses carry different peripherals ,APB1 Mount low-speed peripherals ,APB2 and AHB Mount High Speed peripherals . Corresponding bus The lowest address is called the base address of the bus , The bus base address is also the address of the first peripheral mounted on the bus . among APB1 The address of the bus is the lowest , Peripherals on the chip start here , Also called peripheral base address .

边栏推荐

- Hibernate generates SQL based on Dialect

- memcached基础10

- Leetcode 785: judgment bipartite graph

- Oracle/PLSQL: NumToYMInterval Function

- Why pass SPIF_ Sendchange flag systemparametersinfo will hang?

- p5.js死亡星球

- Oracle/PLSQL: Rpad Function

- Oracle/PLSQL: Lpad Function

- Oracle/PLSQL: Rtrim Function

- Consumers pursue the iPhone because its cost performance exceeds that of domestic mobile phones

猜你喜欢

Simply learn the entry-level concepts of googlecolab

Google began to roll itself, AI architecture pathways was blessed, and 20billion generation models were launched

What if asreml-r does not converge in operation?

执念斩长河暑期规划

Did your case really pass?

二叉樹oj題目

Flink学习5:工作原理

Browser cache

“所有专业都在劝退”,对大学生最友好的竟然是它?

Is the division of each capability domain of Dama, dcmm and other data management frameworks reasonable? Is there internal logic?

随机推荐

达梦数据库的卸载

Detailed explanation of ThreadLocal

paddlepaddle 19 动态修改模型的最后一层

宁愿去996也不要待业在家啦!24岁,失业7个月,比上班更惨的,是没班可上

Config in UVM_ How to use the DB mechanism

memcached基础11

Oracle/PLSQL: HexToRaw Function

lottie. JS creative switch button animal head

XSS攻击(笔记)

图论知识及其应用初步调研

UVM in UVM_ config_ Use of DB in sequence

three.js多米诺骨牌js特效

Parameter estimation -- Chapter 7 study report of probability theory and mathematical statistics (point estimation)

DAMA、DCMM等数据管理框架各个能力域的划分是否合理?有内在逻辑吗?

bluecms代码审计入门

pytorch 23 hook的使用与介绍 及基于hook实现即插即用的DropBlock

Oracle/PLSQL: From_Tz function

Why pass SPIF_ Sendchange flag systemparametersinfo will hang?

How does the C # TCP server limit the number of connections to the same IP?

Why divide the training set and the test set before normalization?