当前位置:网站首页>[digital ic/fpga] detect the position of the last matching sequence

[digital ic/fpga] detect the position of the last matching sequence

2022-06-27 23:52:00 【FPGA silicon agriculture】

Title Description

Write a module , Enter a 64 Bit stream of bits , Identify and match out 101101 The last position of , And output position information .

Code

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/06/21 10:34:41

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module top(

input logic clk,

input logic rst,

input logic valid,

input logic din,

output logic done,

output logic [5:0] pos

);

//101101

logic [5:0] shift_reg;

logic [5:0] cnt;

//cnt

[email protected](posedge clk,posedge rst)

if(rst)

cnt<=0;

else if(valid)

begin

if(cnt==64-1)

cnt<=0;

else

cnt<=cnt+1;

end

//shift_reg

[email protected](posedge clk,posedge rst)

if(rst)

shift_reg<=0;

else if(valid)

shift_reg<={

shift_reg[4:0],din}; // High order input first

//pos

[email protected](posedge clk,posedge rst)

if(rst)

begin

pos<=64;

end

else if(shift_reg==6'b101101)

begin

pos<=cnt-6;

end

//done

[email protected](posedge clk,posedge rst)

if(rst)

done<=0;

else

done<=(cnt==64-1&&valid)?1:0;

endmodule

Test platform

module test;

logic clk;

logic rst;

logic valid;

logic din;

logic done;

logic [5:0] cnt;

logic [5:0] pos;

logic [63:0] data;

//

initial

begin

//data={12'b101101101101,52'd0};

data={

20'd0,12'b101101101101,32'd0};

end

//clk

initial

begin

clk=0;

forever

#5 clk=~clk;

end

//rst

initial

begin

rst=1;

#100

rst=0;

end

//valid,din

initial

begin

valid<=0;

cnt<=0;

wait(rst==1'b0);

@(posedge clk);

repeat(64)

begin

valid<=1;

din<=data[63-cnt];

cnt<=cnt+1;

@(posedge clk);

end

valid<=0;

end

top U(.*);

/* input logic clk, input logic rst, input logic valid, input logic din, output logic done, output logic [5:0] pos ); */

endmodule

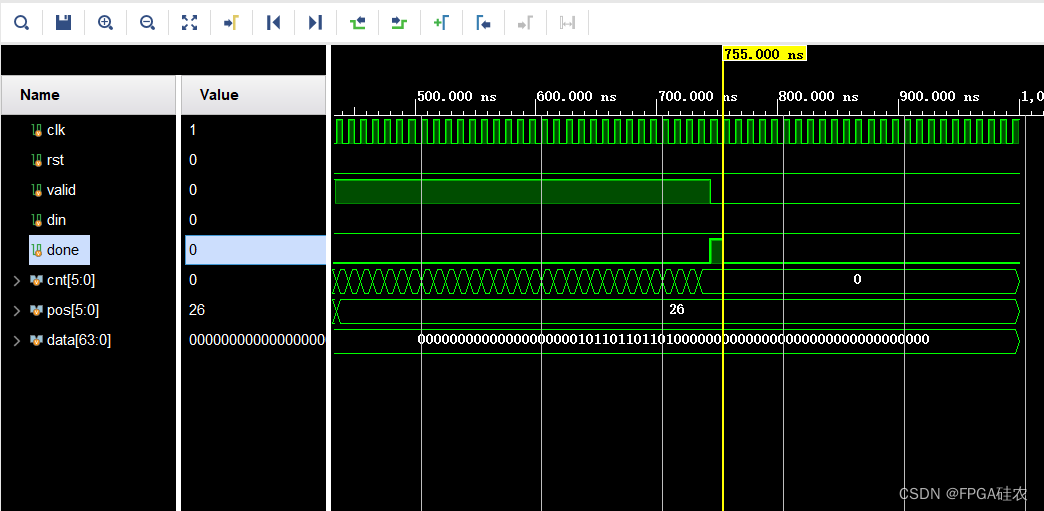

result

Input bitstream is data={20’d0,12’b101101101101,32’d0}, therefore , The position of the last matching sequence should be 20+6=26, In line with expectations .

边栏推荐

- Online JSON to plaintext tool

- [PCL self study: pclplotter] pclplotter draws data analysis chart

- Zero foundation self-study SQL course | complete collection of date functions in SQL

- Storage structure of graph

- Golang - the difference between new and make

- Halcon's region: features of multiple regions (6)

- Course strategy sharing plan of Zhejiang University

- [PCL self study: pclvisualizer] point cloud visualization tool pclvisualizer

- MySQL read / write separation configuration

- fiddler 监听不到接口怎么办

猜你喜欢

随机推荐

Stream + Nacos

Vivado FFT IP的使用说明

【AI应用】NVIDIA Tesla V100-PCIE-32GB的详情参数

小芯片chiplet技术杂谈

ASP.NET仓库进销存ERP管理系统源码 ERP小程序源码

撰写外文时怎样引用中文文献?

沉寂了一段时间 ,我又出来啦~

[PCL self study: pclplotter] pclplotter draws data analysis chart

良/恶性乳腺肿瘤预测(逻辑回归分类器)

C WinForm reads the resources picture

C language character pointer and string initialization

VirtualBox extended dynamic disk size pit

golang使用mongo-driver操作——查(基础)

c语言之字符串数组

An analysis of C language functions

golang - new和make的区别

【Vim】使用教程,常用命令,高效使用Vim编辑器

Swing UI——容器(一)

发射,接收天线方向图

Practice torch FX: pytorch based model optimization quantization artifact