当前位置:网站首页>嵌入式virlog代码运行流程

嵌入式virlog代码运行流程

2022-06-26 12:41:00 【修服】

基于vivado的virlog运行流程(Nexys A7开发板)

嵌入式virlog代码运行流程

一、新建工程

使用的芯片是Artix芯片,Nexys A7开发板。

1.设置项目名称和存储路径

2.一般使用RTL类型,如果没有想要添加的文件,可以勾选

下面的方框选项

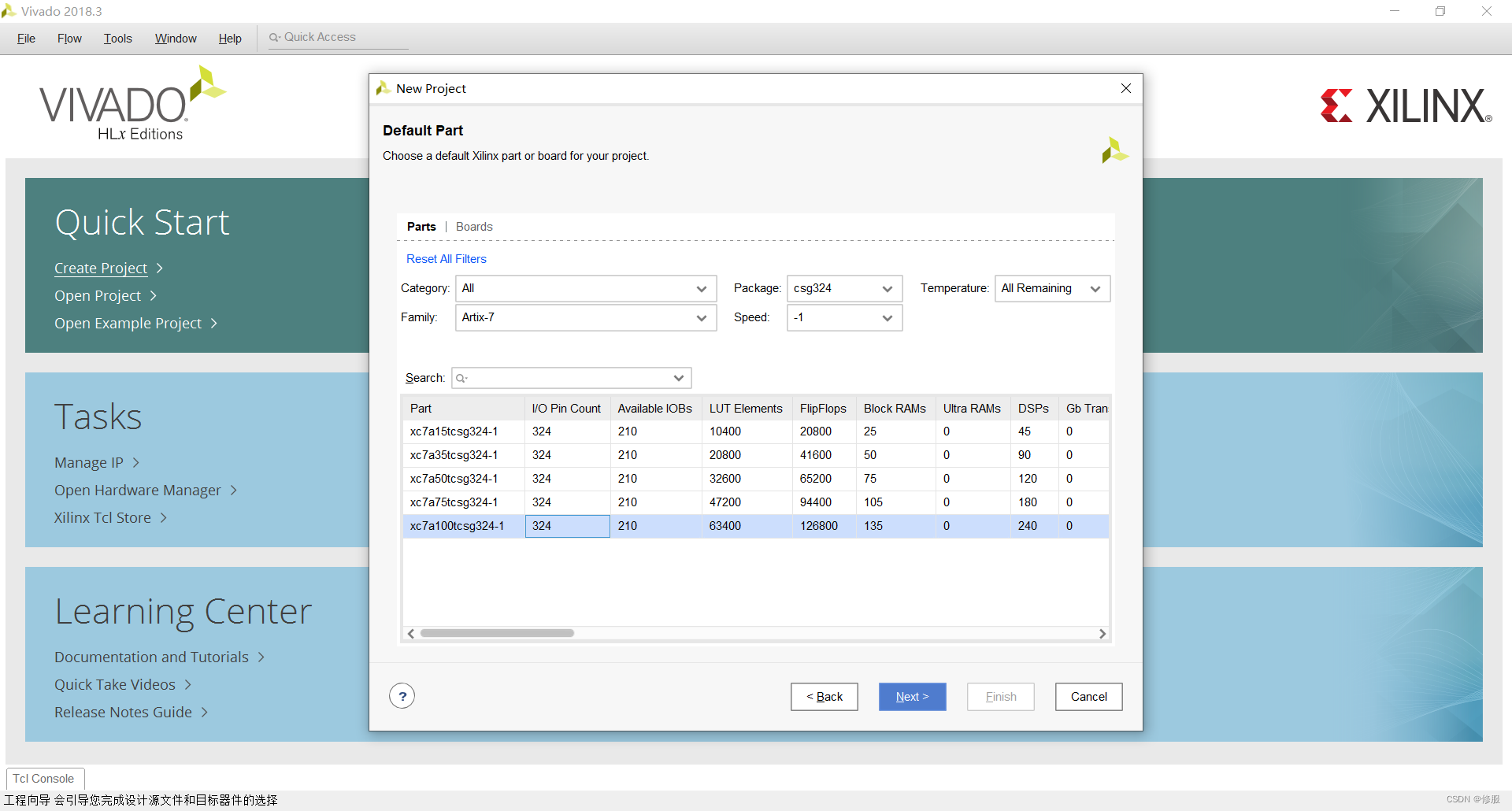

3.在这里可以使用下拉框添加芯片的搜索选项,根据需要选择

4.finish

二、设计输入和综合

代码结构为:

design:设计文件

constraints:约束文件

Simuation:仿真文件

1.输入设计

增加design代码

代码如下:

module add(a,b,c,y);

input a,b,c;

output y;

assign y=~(a&b&c);

endmodule

2.进行综合

三、进行仿真

添加Simulation代码

代码如下(示例):

module add_sim( );

parameter N=3;//是几变量输入,n就是几

reg clk=0;

reg [N-1:0] cnt;

wire a,b,c;

wire y;//输入输出的线口

always #10 clk=~clk;

[email protected](posedge clk)

begin

cnt=cnt+1'b1;

end

//在上升沿把cnt+1=cnt

initial

begin

cnt=3'b0;//3表示位元,0表示数值,b表示二进制

end

assign {

a,b,c}=cnt;//cnt给a,b,c满量程变化,拼接运算符

add utest(a,b,c,y);

endmodule

仿真:

行为仿真

功能仿真

时序仿真

不同的仿真会有不同的波形图效果

四、进行约束

先了解板子的引脚资源

1.约束向导方式配置资源

2.IO planning方式配置引脚,这里我使用IO方式配置

在板子资源中寻找资源对应的引脚名称,在ports中设置,IO std发红就选择其它黑色的类型

这里J15,L16,M13对应拨码开关;H17对应发光二极管

保存约束文件

五、实现和下载

进行综合生成比特流

在上一步运行完成后,BitStream就会变绿,点击它生成位图文件

在这里打开板子,打开成功后会出现program的选择,点击后再点击出现的program就可以在板子上运行了

边栏推荐

- Reflect the technical depth (unable to speed up)

- 适配器模式(Adapter)

- 【Spark】. Explanation of several icons of scala file in idea

- Es snapshot based data backup and restore

- MySQL数据库讲解(四)

- 外观模式(Facade)

- Word document export (using fixed template)

- tauri vs electron

- Echart stack histogram: add white spacing effect setting between color blocks

- Enjoy element mode (flyweight)

猜你喜欢

May product upgrade observation station

Here Document免交互及Expect自动化交互

![[how to connect the network] Chapter 2 (Part 1): establish a connection, transmit data, and disconnect](/img/e3/a666ba2f48e8edcc7db80503a6156d.png)

[how to connect the network] Chapter 2 (Part 1): establish a connection, transmit data, and disconnect

MongoDB系列之Window环境部署配置

Basic methods for network diagnosis and hardware troubleshooting of Beifu EtherCAT module

【Spark】. Explanation of several icons of scala file in idea

Basic configuration and test of Beifu twincat3 NCI in NC axis interface

去某东面试遇到并发编程问题:如何安全地中断一个正在运行的线程

网络远程访问的方式使用树莓派

shell脚本详细介绍(四)

随机推荐

Awk tools

MySQL数据库讲解(三)

防火墙介绍

Mysql database explanation (6)

Learning Processing Zoog

Beifu PLC realizes data power-off maintenance based on cx5130

ES6 module

去某东面试遇到并发编程问题:如何安全地中断一个正在运行的线程

7-3 minimum toll

Basic methods for network diagnosis and hardware troubleshooting of Beifu EtherCAT module

Zoomeeper sets ACL permission control (only specific IP access is allowed to enhance security)

Electron official docs series: Best Practices

ES基於Snapshot(快照)的數據備份和還原

Decorator

5+api, clear application cache

IDC report: the AI cloud market share of Baidu AI Cloud ranks first for six consecutive times

装饰器(Decorator)

H5视频自动播放和循环播放

A collection of common tools for making we media videos

HDU 3709 Balanced Number