当前位置:网站首页>Localization SoC development plan

Localization SoC development plan

2022-06-28 07:39:00 【youbin2013】

Localization SOC Development plan

1 be familiar with SOC And the use of the development suite

At this stage, localization has just been achieved SOC The initial stages of the development board , The work to be completed at this stage includes :

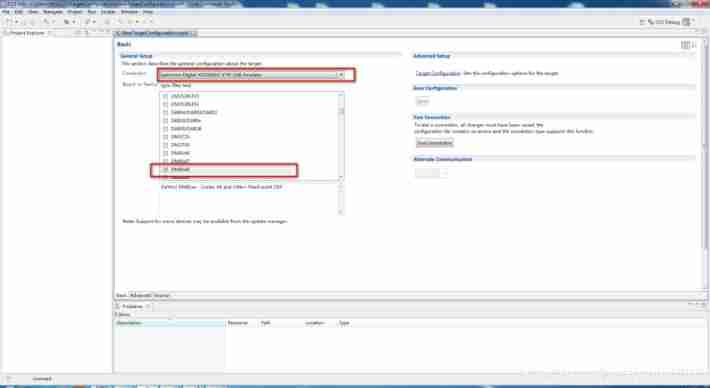

1, Install the development kit , And learn to use the development kit , And be able to conduct power on commissioning ;

2, Go through the schematic diagram of the development board roughly , See which peripherals need to be driven by development , And the whole SOC Chip corresponding pin distribution , And the protection, power distribution and power on requirements of important devices ;

3, Go through the development manual , Understand the function overview and architecture of the chip , Understand its internal composition through the chip architecture diagram , Evaluation of core performance , Bus connection relationship and clock distribution .

The development time of this stage is estimated to be about 3 Days or so .

2 debugging SOC Related peripherals

This stage is mainly to design the peripheral driver of the chip , And test the driver function completed by yourself . After the functional debugging is completed, it is also necessary to complete the specification encapsulation , This is a convenient driver to use . Through the data manual, we can know that the peripherals of the chip mainly include :

- Chip clock configuration , It mainly configures the frequency doubling and frequency division of the internal phase-locked loop of the chip , It is used to provide the chip core clock and all peripheral clocks ;

cycle : Development time and debugging time :1 God .

- Chip timer and interrupt configuration , It is mainly used to complete the implementation of timer interrupt , It can provide precise timing in the application layer ;

cycle : The development time and debugging time without problems are 3 God ( Timer configuration 1 God , interrupt 2 God ), If something goes wrong, you may need to 4-5 Days or more .

- GPIO Port configuration , It is mainly used to complete the input and output functions of discrete quantities ;

cycle : The development time and debugging time without problems are 1 God , If something goes wrong, you may need to 2-3 Days or more .

- UART Configuration of peripherals , It is mainly used to complete the communication function of serial port ;

cycle : The development time and debugging time without problems are 2 God , If something goes wrong, you may need to 3-4 God .

- 1553B Bus configuration , Mainly used to complete 1553B Communication function ;

cycle : The development time and debugging time without problems are 3-4 God , If something goes wrong, you may need to 1 Zhou .

- CAN Bus configuration , Mainly used to complete CAN Bus communication function ;

cycle : The development time and debugging time without problems are 2-3 God , If something goes wrong, you may need to 4-5 God .

- QSPI Interface configuration and FLASH Read write driver , Mainly used to complete FLASH Read and write , For program loading .

cycle : The development time and debugging time without problems are 4 God ,(QSPI Interface configuration 2 God ,FLASH Drive design for two days ), If something goes wrong, you may need to 1 Zhou .

- SPI Interface configuration and FLASH Read write driver , Mainly used to complete FLASH Read and write , For program loading .

cycle : The development time and debugging time without problems are 2-3 God , If something goes wrong, you may need to 4-5 God .

- IIC Interface configuration and eeprom Read write driver ,eeprom Used to store power down configuration information ,IIC Interfaces are used to control IIC Interface sensors, etc .

cycle : The development time and debugging time without problems are 2-3 God , When something goes wrong, you may need to 4-5 God .

- DDR3 Configuration of extended memory , It is mainly used to complete the use of extended memory , Use when the on-chip memory is insufficient .

cycle : The development time and debugging time without problems are 3 God , Problems may require 4-5 God .

- DMA Configuration of the controller , It is mainly used to complete the rapid movement of data , stay CPU Complete the data migration of the specified address while working .

cycle : The development time and debugging time without problems are 4-5 God , Problems may require 1 Zhou .

3 Research SOC Start process , Analyze the whole operation process

At this stage, the whole domestic market will be basically SOC With a certain degree of mastery , At this point, you can start to study the startup process of the chip , Mainly internal ARM Program movement of the core and instruction jump , And the file composition of the whole program . In the startup process code , Most of them are assembly files , Need to master some ARM To effectively read its source code , And also master ARM Related architecture of , Be familiar with the configuration of coprocessor and main core to realize interrupt jump and stack building . In the SOC There is another one in the project scatt, The file is similar to zynq Of ld file , But it's very different , These two types of files are files that link memory address allocation and data storage location , You also need to master .

1, Research 771 Start up process provided , Understand the entire startup process , The development cycle may only need 1 Around the week .

2, But I want to modify the memory link file at any time , Modify the startup process code , Complete the application of dual core and the installation of the system , Then we need to study ARM Instruction set and architecture , The development cycle of this process may take more than a few weeks .

边栏推荐

猜你喜欢

Recommended system series (Lecture 5): Optimization Practice of sorting model

Alibaba cloud server creates snapshots and rolls back disks

本周二晚19:00战码先锋第8期直播丨如何多方位参与OpenHarmony开源贡献

Principle and practice of bytecode reference detection

Sentinel mechanism of redis cluster

How to configure DDR3 of dm8148

Design and implementation of spark offline development framework

异或的应用。(提取出数字中最右侧的1,面试中经常用的到)

kubelet垃圾(退出的容器和未使用的镜像)回收源码分析

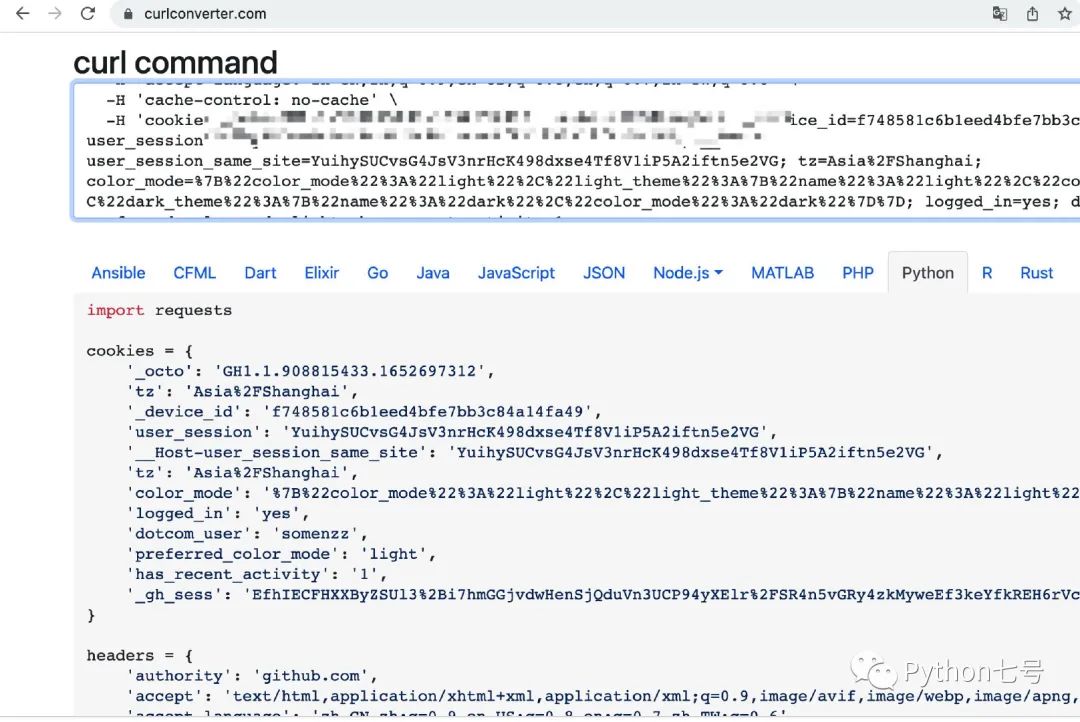

A gadget can write crawlers faster

随机推荐

Evaluation of inverse Polish expression < difficulty coefficient >

阿里云服务器创建快照、回滚磁盘

Disposition Flex

Code submission specification

kubelet驱逐机制的源码分析

kubernetes集群命令行工具kubectl

HJ字符串排序

Kubelet garbage collection (exiting containers and unused images) source code analysis

Real time database - Notes

Hack the box:routerspace

Investment transaction and settlement of the fund

DBeaver 22.1.1 发布,可视化数据库管理平台

NDK cross compilation

Design of DSP image data stream

Sword finger offer II 091 Paint the house

kubelet垃圾(退出的容器和未使用的镜像)回收源码分析

Mysql8.0和Mysql5.0访问jdbc连接

What should I do if the version is incompatible with the jar package conflict?

HJ质数因子

golang gin框架进行分块传输