当前位置:网站首页>Concept of IP, classification of IP, IP multiplexing technology

Concept of IP, classification of IP, IP multiplexing technology

2022-07-24 16:44:00 【Dull as dull】

background :IP Cause of occurrence

With the ultra deep submicron manufacturing technology of integrated circuits 、 The rapid development of design technology , Integrated circuits have entered the era of system on chip . The so-called system on chip refers to the realization of signal acquisition on a single silicon chip 、 transformation 、 Storage 、 Deal with and I/0 And so on , Or digital circuits are integrated on a single silicon chip 、 Analog circuit 、 Signal acquisition and conversion circuit 、 Memory 、 Microprocessor MPU、 Micro controller MCU、 Digital signal processor DSP etc. , Realize the function of a system . SOC can realize high-level system integration on a single silicon chip , But at the same time, it also poses a huge challenge to the design of silicon chips . Because the current design tools and methods are not fully qualified for the design of system on chip . While the complexity of chip design increases rapidly , The growth of skilled designers is limited , And the requirement of design cycle is higher and higher .

IP Multiplexing technology , It is to improve the efficiency of system on chip design 、 A key to shortening the design cycle .

IP There are three advantages of multiplexing technology :

- Repeated use IP It can improve the design ability , Save designers , It is one of the most effective ways to bridge the gap between the design and manufacture of integrated circuits ;

- It can greatly shorten the listing cycle ;

- We can make better use of the existing technology , cost reduction .

Expected in the next few years ,50% The above system on chip design should be reusable to varying degrees IP Based on the kernel of .

Reuse is not a new concept . In the field of software design , Reusable code has been used for a long time , Such as function library, etc , To improve design efficiency . In recent years , In the field of hardware design IP Reuse technology has made a major breakthrough . Automatic synthesis tool and hardware description language HDL (Hardware Description Language) Together, design reuse will be promoted to a higher level of abstraction , Realize the automation of design reuse , At the same time, it improves the efficiency and quality of the design .HDL It can realize the modularization of design 、 A parameterized , Facilitate the selection of sub modules 、 Operations such as adding and arranging . The automatic synthesis tool optimizes the design according to the specific application and directly maps to the corresponding process library . By the above means , Greatly enhanced IP The reusability of . Hardware design reuse is gradually adopting software methods , Such as programming 、 compile 、 Library technology, etc , From hardware design mode to software design mode .

IP The concept of

IP(Intellectual Property) It has intellectual property rights 、 Has been designed and verified 、 Reusable integrated circuit modules .

IP The classification of

According to different design levels , IP It is divided into soft core 、 Hard core and solid core .

- Soft core can be integrated HDL describe . Soft core includes logical description (RTL And gate level Verilog HDL or VHDL Code )、 Device internal wiring table and testability design . The soft core can be modified by the user , To achieve the required circuit system design . It is mainly used for interfaces 、 code 、 decoding 、 Algorithms, channel encryption and other complex systems that require a wide range of speed performance . The development workload of soft core is relatively low , Therefore, the development cost is generally low , Flexible , For example, features can be added or processes can be selected, and it is easy to transfer from one process to another , And the performance can be improved , But the predictability is poor .

- Hard core is chip layout . The design and process of hard core have been completed and cannot be changed . The hard core that users get is only product function, not product design , therefore , The design and manufacturer of hard core can exercise full control over it , Its intellectual property protection is also relatively simple . The commonly used hard core is memory 、 Analog devices and bus devices . The development cost of hard core is the highest , Small flexibility , But the performance must be predictable , Easy to use .

- Solid core is gate level HDL describe . Solid core is between soft core and hard core IP. It is neither independent , It's not fixed , Some modifications can be made according to user requirements . Fixed core allows users to redefine key performance parameters , Some internal connection tables can be re optimized , Its use process is the same as that of soft core . If the internal connection table cannot be optimized , The use process is the same as that of hard core . Solid core is between hard core and soft core .

More typical IP Yes : MPEG nucleus ( Image market )、 Memory core 、SPARC(RISC Microprocessor ) Nuclear, etc .

IP Multiplexing technology

IP Multiplexing technology , That is, reuse the integrated circuit that has been designed and verified IC modular , It is to improve the efficiency of system on chip design 、 A key to shortening the design cycle .

Remark knowledge

HDL (Hardware Description Language)

Verilog HDL

VHSIC (very-high-speed integrated circuits)

VHDL (VHSIC Hardware Description Language) The difference in Verilog It's another language , It seems that no one uses it anymore

reference

边栏推荐

- Getting started with arcpy

- Qualcomm reconciled with apple and received at least $4.5 billion in settlement fees! Next goal: Huawei!

- Win10 download address

- regular expression

- 为什么被调函数内部不能用 sizeof(arr) / size(arr[0]) 计算数组长度?

- Mysql增删改查、检索与约束(详细教学)

- File browser? QT can also be achieved!

- Due to lack of funds, Changdian technology sold some assets of Xingke Jinpeng for 120million US dollars!

- EF data migration

- EF miscellaneous

猜你喜欢

Jing Wei PS tutorial: basic part a

Envi SHP to ROI and mask the grid

ArcGIS pixel size changed from 0.00025 to meters

![为什么被调函数内部不能用 sizeof(arr) / size(arr[0]) 计算数组长度?](/img/e6/1d2213f3eb9bd0ff537a66d2b01f98.png)

为什么被调函数内部不能用 sizeof(arr) / size(arr[0]) 计算数组长度?

PS pull out logo

ARP 入门

Jupyter uses tips

Long awaited full platform support - Open Source im project uniapp update of openim

IP第十三天笔记

Sword finger offer 48. the longest substring without repeated characters

随机推荐

709. Convert to lowercase letters

SS-Paper【1】:Fully Convolutional Networks for Semantic Segmentation

IP的概念,IP的分类,IP复用技术

Qt键盘事件(一)——检测按键输入

With notes: printing order of synchronous, asynchronous, micro task and macro task

"Heaven and the world, self-respect" -- single case mode

ArcGIS pixel size changed from 0.00025 to meters

百度推广“删除重提”是什么意思?

Hping3 installation and use

Disassembly of Samsung Galaxy fold: the interior is extremely complex. Is the hinge the main cause of screen damage?

2019q1 global smartphone shipments: Huawei vivo increased significantly, while Apple plummeted 30.2%!

Getting started with arcpy

Enter a URL to this page to show it. What happened in this process?

Jenkins CLI 命令详解

C font usage effect

MODIS 16 day data monthly / quarterly synthesis

EF LINQ Miscellany

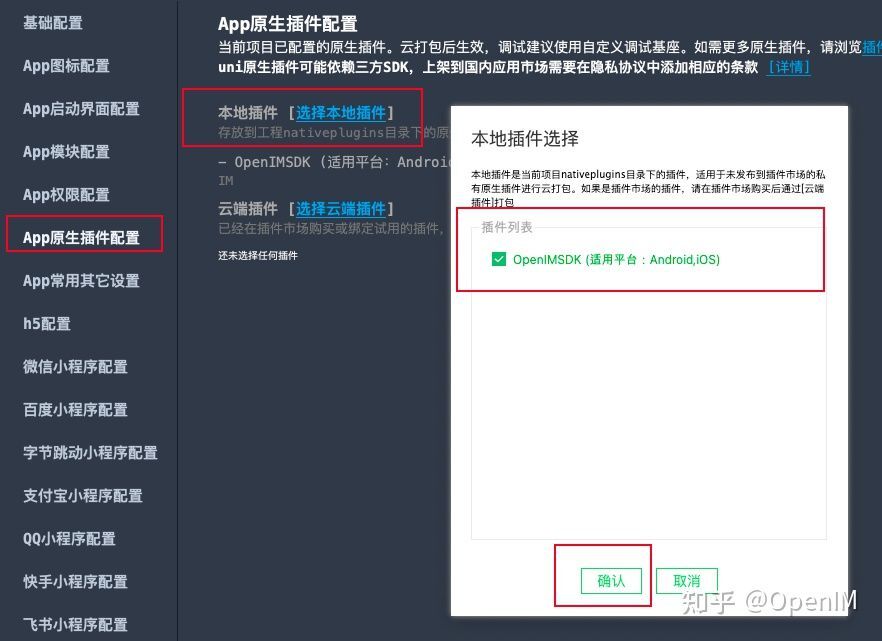

【技术】uniapp之聊天室 demo

IP第十三天笔记

1184. 公交站间的距离